Altera MAX 10 Embedded Memory User Manual

Page 68

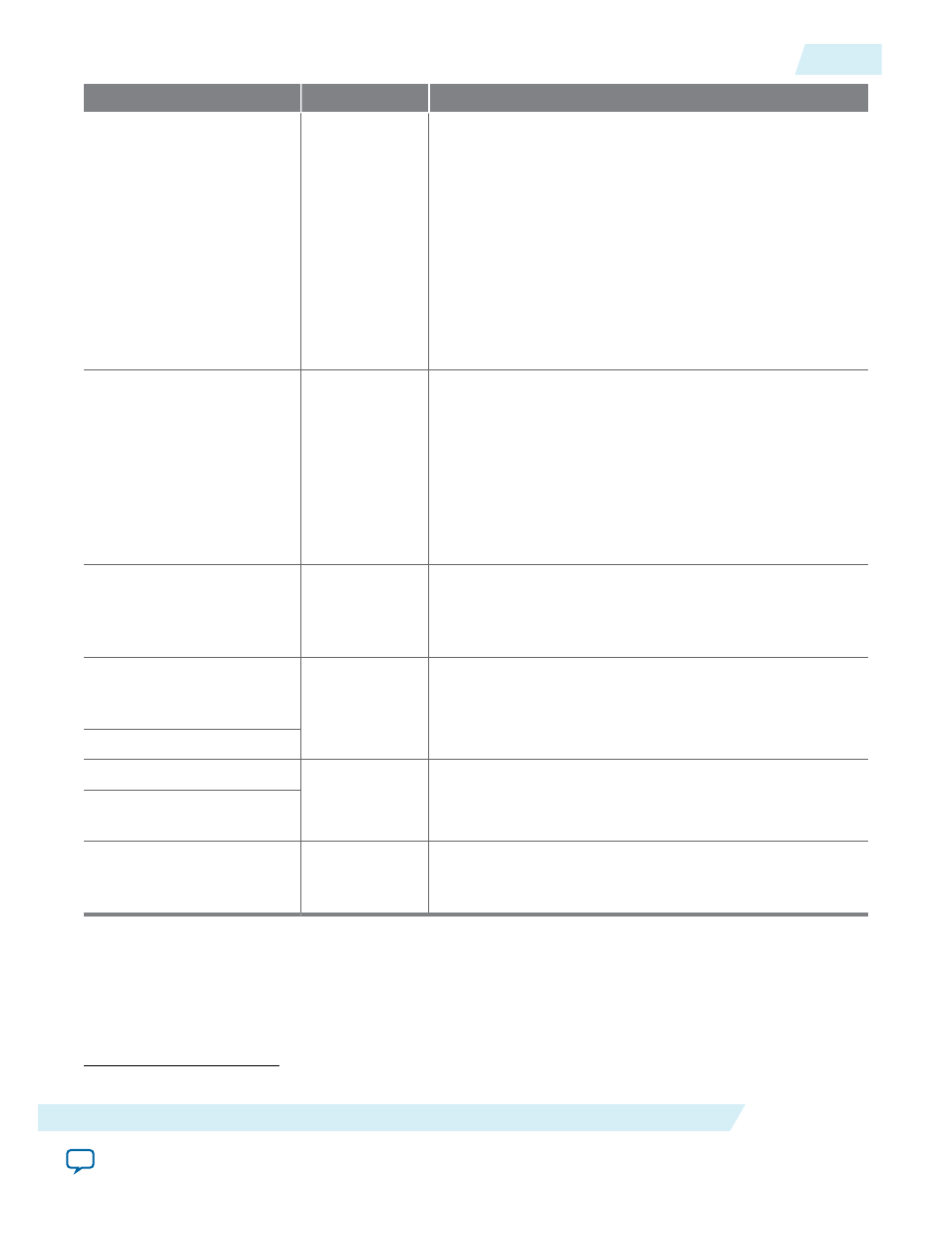

Parameter

HDL Parameter

Description

Which type of optimiza‐

tion do you want?

(2)

clocks_are_

synchronized

Specifies whether or not the write and read clocks are

synchronized, which in turn determines the number of

internal synchronization stages added for stable operation

of the FIFO. The values are TRUE and FALSE. If omitted,

the default value is FALSE. You must only set the

parameter to TRUE if the write clock and the read clock

are always synchronized and they are multiples of each

other. Otherwise, set this to FALSE to avoid metastability

problems. If the clocks are not synchronized, set the

parameter to FALSE, and use the rdsync_delaypipe and

wrsync_delaypipe parameters to determine the number of

synchronization stages required.

What should the memory

block type be

ram_block_type

Specifies the target device’s memory block to be used. To

get the proper implementation based on the RAM configu‐

ration that you set, allow the Quartus II software to

automatically choose the memory type by ignoring this

parameter and turn on the Implement FIFO storage with

logic cells only, even if the device contains memory

blocks. parameter. This gives the Compiler the flexibility

to place the memory function in any available memory

resource based on the FIFO depth required.

Would you like to

register the output to

maximize the perform‐

ance but use more area?

(3)

add_ram_

output_

register

Specifies whether to register the q output. The values are

Yes (best speed) and No (smallest area). The default value

is No (smallest area).

Becomes true when

usedw[] is greater than or

equal to:

(3)

almost_full_

value

Sets the threshold value for the almost_full port. When the

number of words stored in the FIFO IP core is greater than

or equal to this value, the almost_full port is asserted.

Almost full

(3)

Almost empty

(3)

almost_empty_

value

Sets the threshold value for the almost_empty port. When

the number of words stored in the FIFO IP core is less than

this value, the almost_empty port is asserted.

Becomes true when

usedw[] is less than:

(3)

Currently selected device

family

intended_

device_family

Specifies the intended device that matches the device set in

your Quartus II project. Use this parameter only for

functional simulation.

(3)

Applicable in SCFIFO mode only.

UG-M10MEMORY

2015.05.04

FIFO IP Core Parameters for MAX 10 Devices

9-7

FIFO IP Core References

Altera Corporation