Max 10 embedded memory clock modes, Asynchronous clear in clock modes, Max 10 embedded memory clock modes -9 – Altera MAX 10 Embedded Memory User Manual

Page 13: Asynchronous clear in clock modes -9

Related Information

MAX 10 Embedded Memory Related IPs

MAX 10 Embedded Memory Clock Modes

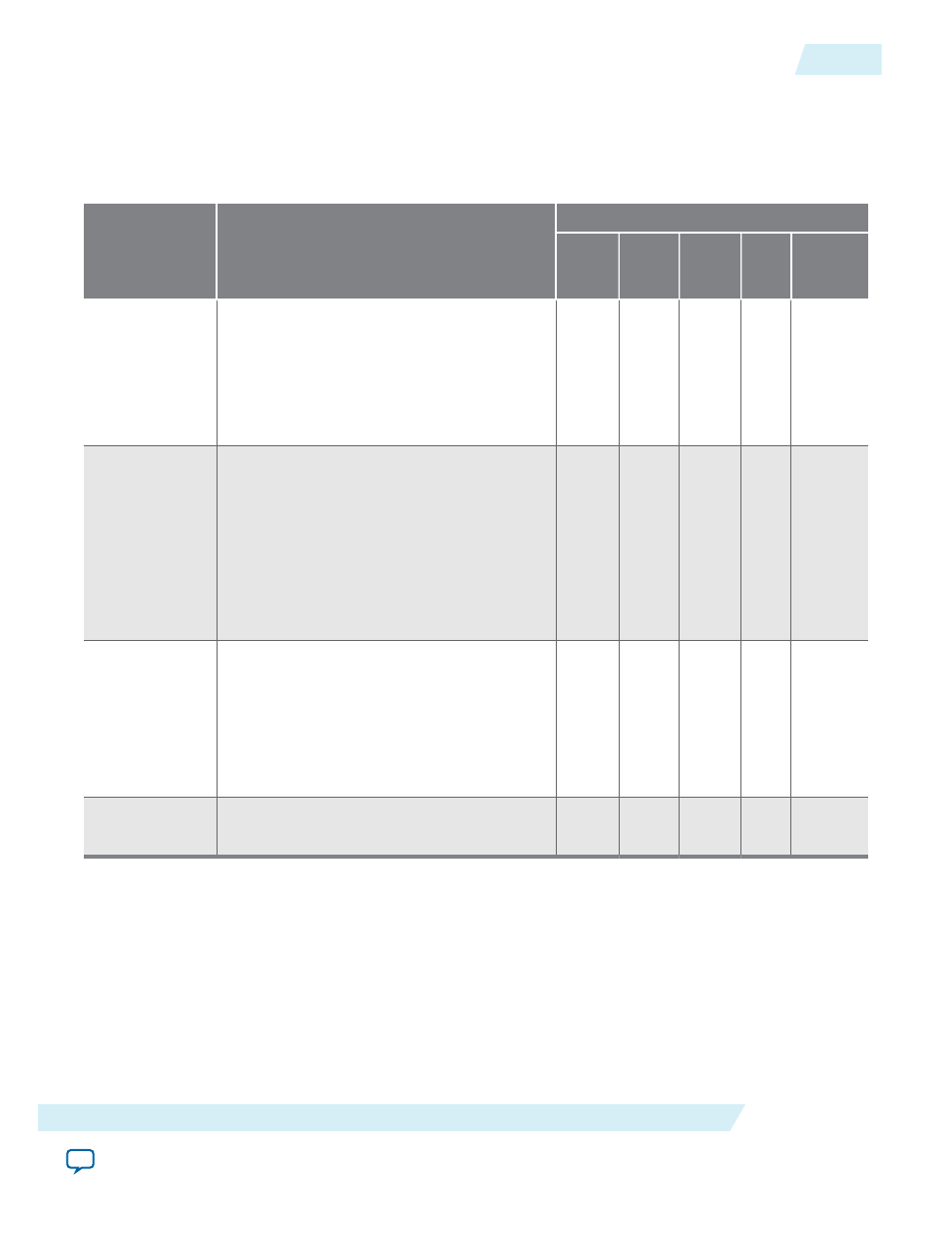

Clock Mode

Description

Modes

True

Dual-

Port

Simple

Dual-

Port

Single-

Port

ROM

FIFO

Independent

Clock Mode

A separate clock is available for the following

ports:

• Port A—Clock A controls all registers on the

port A side.

• Port B—Clock B controls all registers on the

port B side.

Yes

—

—

Yes

—

Input/Output

Clock Mode

• M9K memory blocks can implement input

or output clock mode for single-port, true

dual-port, and simple dual-port memory

modes.

• An input clock controls all input registers to

the memory block, including

data

,

address

,

byteena

,

wren

, and

rden

registers.

• An output clock controls the data-output

registers.

Yes

Yes

Yes

Yes

—

Read or Write

Clock Mode

• M9K memory blocks support independent

clock enables for both the read and write

clocks.

• A read clock controls the data outputs, read

address, and read enable registers.

• A write clock controls the data inputs, write

address, and write enable registers.

—

Yes

—

—

Yes

Single-Clock

Mode

A single clock, together with a clock enable,

controls all registers of the memory block.

Yes

Yes

Yes

Yes

Yes

Related Information

•

•

Control Clocking to Reduce Power Consumption

•

Output Read Data in Simultaneous Read and Write

on page 2-10

Asynchronous Clear in Clock Modes

In all clock modes, asynchronous clear is available only for output latches and output registers. For

independent clock mode, this is applicable on port A and port B.

UG-M10MEMORY

2015.05.04

MAX 10 Embedded Memory Clock Modes

2-9

MAX 10 Embedded Memory Architecture and Features

Altera Corporation