Rockwell Automation 1775-S4B,D17756.5.3 User Manual SCANNER/MSG HND User Manual

Page 149

Floating Point Values on the 1775ĆS4B Scanner

Appendix B

BĆ8

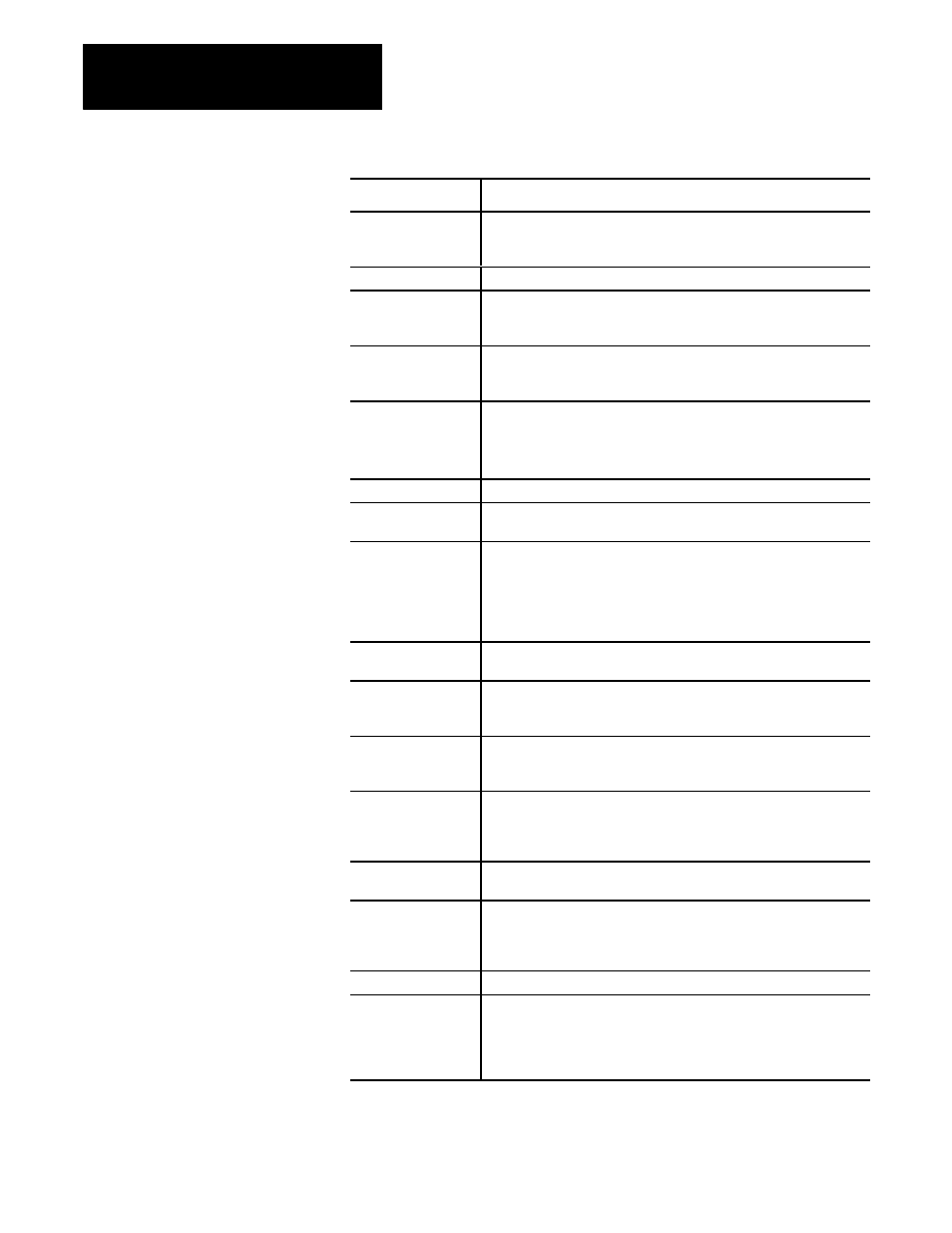

Rung Number

Description

RM0:

Whenever there is not a conversion fault and whenever F0:0 does not

equal 0 (i.e., F0:0 changes value) reset the oneĆshot bit and

jumpĆtoĆsubroutine.

RM1:

End of program for main program section.

RS0:

If F0:0 is less than 0 (negative), negate F0:0 and latch on the negate

result flag bit. This rung allows us to work on only positive floating point

numbers.

RS1:

If the oneĆshot bit is not on (reset by RM0) move F0:0 to F0:2, turn on the

oneĆshot bit, reset counters C0Ć2 and unlatch the conversion complete

bit.

RS2:

If 1EĆ38 <= F0:2 <= EĆ1 (essentially Ćinfinity and 1), multiply F0:2 by 10

and latch the multiply flag bit. Store result in F0:2.

In range is defined in rung RS6 (essentially 1 to 10 or X EO). If FO:2 is

multiplied by 10, it becomes closer to being in range.

RS3:

Unconditional watchdog counter C2 must have a preset of 40.

RS4:

If watchdog counter C2 counts out (ACC = PRE), jump to label 5 (rung

RS18).

RS5:

If F0:2 > 9.99999 E0, (essentially 10 to +infinity), divide F0:2 by 10 and

latch the devide flag bit. Store the result in F0:2.

In range is defined in rung RS6 (essentially 1 to 10 or X E0). If F0:2 is

divided by 10, it becomes closer to being in range.

Rungs RS2 and RS5 are mutually exclusive.

RS6:

If 1 E0 <= F0:2 <= 9.99999 E0, F0:2 is in range and B0:0/L is latched on

to indicate that the conversion is complete.

RS7:

If a multiplication was performed in rung RS2, count that occurrence. This

keeps track of how many times we multiply F0:2 by 10 before it comes

into range. The less than range counter C0 is incremented.

RS8:

If a division was performed in rung RS5, count that occurrence. This

keeps track of how many times we divide F0:2 by 10 before it comes into

range. The greater than range counter Cl is incremented.

RS9:

Unlatches the multiply and divide flag bits and also unlatches the enable

bits of counters C0, Cl, and C2. This is necessary so that when we jump

back to label 4, the counters will be able to increment properly (they must

see a falseĆtoĆtrue transition to increment).

RS10:

If the conversion is not complete, jump back to label 4 and repeat

process until value falls into range.

RS11:

This rung is only executed when the value is in range. The value is

moved into N0:0. This strips off the fractional part. N0:0 is subtracted

from F0:2. F0:3 now contains only the fractional part. Due to rounding, if

F0:3 > 0, N0:0 is decremented by 1.

RS12:

Calculates the fractional part of the number and places it into H0:1.

RS13:

When the conversion is complete, move F0:0 into F0:1 making the two

values equal. This will prevent any further jumps to subroutine (rung

RM0) unless the value of F0:0 changes. Also, if the negate result flag bit

is set, negate the integer result stored in H0:0 and reset the negate result

flag bit.