Expanded math operations – Rockwell Automation 1772-LS_LSP,D17726.8.6 PROG/OPER MANUAL-MINI PLC-2/05 User Manual

Page 99

Math Instructions

Chapter 10

10Ć11

Expanded Math Operations

Your processor executes the following expanded math operations and maintains

the proper sign of the result:

addition

subtraction

multiplication

division

BCD to binary conversion

Binary to BCD conversion

square root (not a signed function)

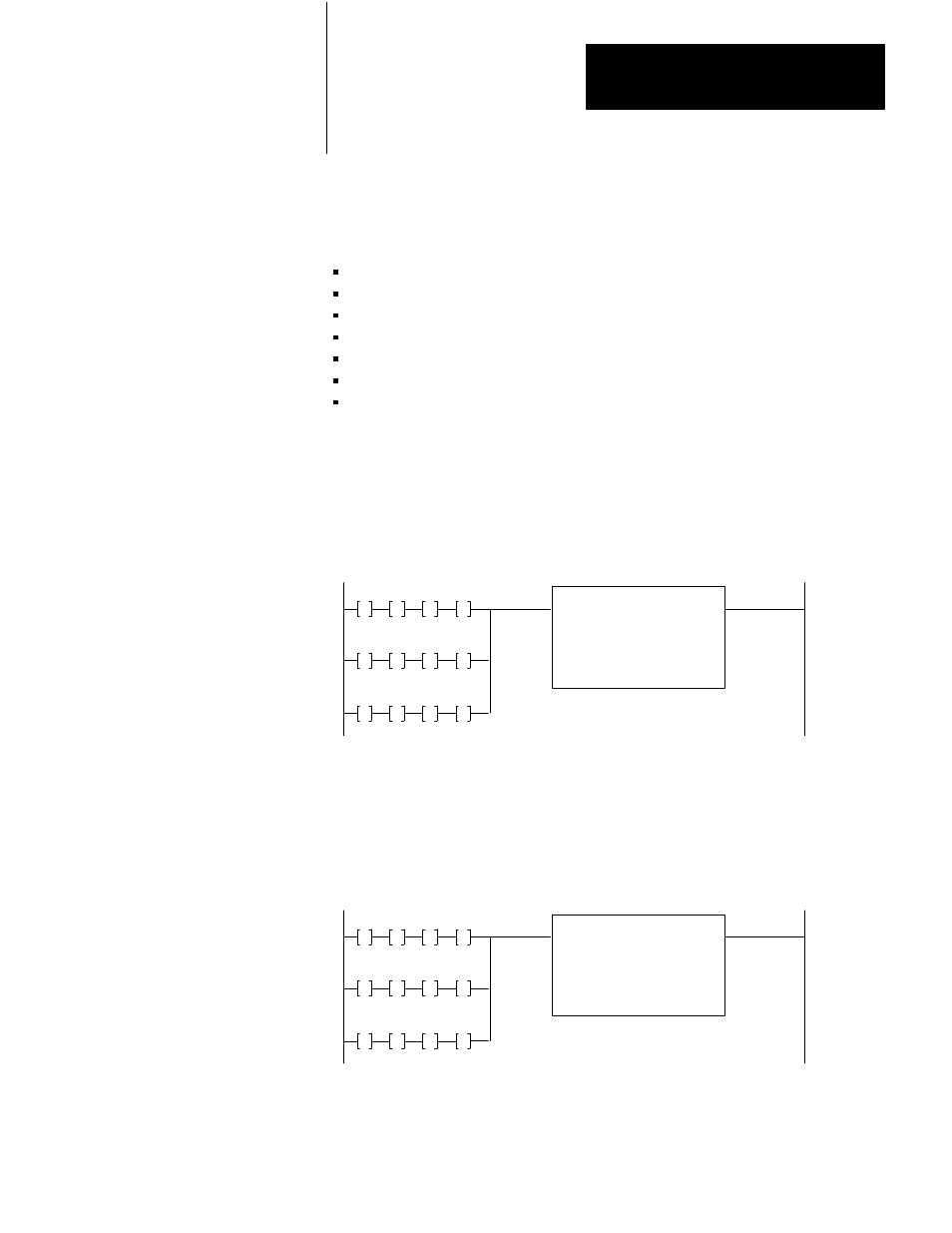

Addition, Subtraction, Multiplication, and Division

Addition

Reports the sum (result address) of the augend (operand A, the data address)

and the addend (operand B, the conditioning gets). The addition function uses

up to 12 digits for each operand. When the sum exceeds 999 999.999 999, the

overflow bit (bit 14) in the result address word is set.

060

000

G

061

000

G

062

000

G

063

000

G

Executive Aux

Function

Function Number:

Data Addr:

Result Addr:

01

040

060

Start

050

000

G

051

000

G

052

000

G

053

000

G

040

000

G

041

000

G

042

000

G

043

000

G

Important: If an overflow value is used for subsequent comparisons or other

arithmetic operations, inaccurate results could occur.

Subtraction

Reports the difference (result address) between two operands, a minuend (data

address) and subtrahend (conditioning gets). The operands can use up to

12 digits.

060

000

G

061

000

G

062

000

G

063

000

G

Executive Aux

Function

Function Number:

Data Addr:

Result Addr:

02

040

060

Start

050

000

G

051

000

G

052

000

G

053

000

G

040

000

G

041

000

G

042

000

G

043

000

G