Cirrus Logic CS4953xx User Manual

Page 87

8-9

Copyright 2010 Cirrus Logic, Inc.

DS732UM10

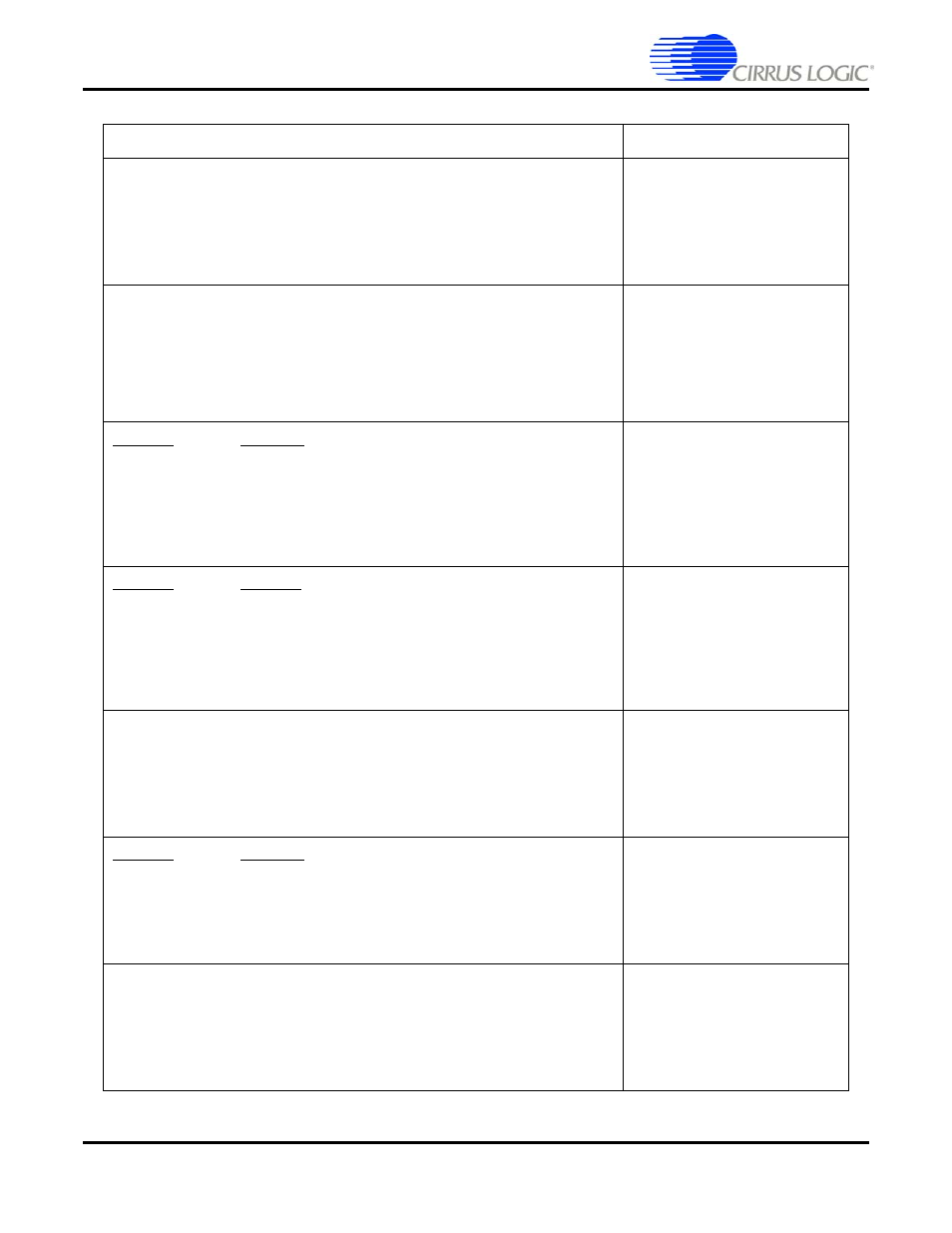

SDRAM/Flash Controller Interface

CS4953xx Hardware User’s Manual

§§

StaticWaitTurn0

(Not Supported)

Bus Turnaround Cycle Delay (t

xmturn

)

Bit 31:4 = 0 = Reserved

Bit 3:0 =SRAM_TURN_CYCLE, where:

0000 to 1110 = (n+1) HCLK cycle for bus Turnaround time.

t

xmturn

=(SRAM_TURN_CYCLE + 1)*HCLK

0x81000076

0xHHHHHHHH

Default 0x0000000F

StaticConfig1

Bit 31:2 = 0 = Reserved

Bit 1:0 = Memory Bus Width, where:

00 = Flash Memory bus 8 bits wide.

01 = Flash Memory bus 16 bits wide.

10 = Reserved

11 = Reserved

0x81000077

0xhHHHHHHH

Default 0x00000001

StaticWaitWen1

EXT_CS falling to EXT_WE falling (t

xmcswe

)

Bit 31:4 = 0 = Reserved

Bit 3:0 = Flash_WEN_CYCLE, where:

0000 = one DSP clk cycle between the assertion of chip select and write

enable. 0001 to 1111 = (n+1) cycle delay.

t

xmcswe

=(Flash_WEN_CYCLE + 1 )*HCLK

0x81000078

0XHHHHHHHH

Default 0x00000000

StaticWaitOen1

EXT_CS falling to EXT_OE falling (t

xmcsoe

)

Bit 31:4 = 0 = Reserved

Bit 3:0 =Flash_OEN_CYCLE, where:

0000 = no delay between the assertion of chip select and output enable.

0001 to 1111 = (n) cycle delay.

t

xmcsoe

=(Flash_OEN_CYCLE )*HCLK

0x81000079

0xHHHHHHHH

Default 0x00000000

StaticWaitRd1

Single Word Read Cycle (t

xmrdc

)

Bit 31:5 = 0 = Reserved

Bit 4:0 =Flash_RD_CYCLE, where:

00000 to 11110 = (n+1) HCLK cycle for Read Cycle.

t

xmrdc

=(Flash_RD_CYCLE + 1 )*HCLK - 6.87ns

0x8100007A

0xHHHHHHHH

Default 0x0000000A

StaticWaitWr1

EXT_CS falling to EXT_WE rising (t

xmcswa

)

Bit 31:5 = 0 = Reserved

Bit 4:0 =Flash_WR_CYCLE, where:

00000 to 11110 = (n+2) HCLK cycle for Write access time.

t

xmcswa

=(Flash_WR_CYCLE + 2)*HCLK

0x8100007C

0xHHHHHHHH

Default 0x00000007

StaticWaitTurn1

Bus Turnaround Cycle Delay (t

xmturn

)

Bit 31:4 = 0 = Reserved

Bit 3:0 =Flash_TURN_CYCLE, where:

0000 to 1110 = (n+1) HCLK cycle for bus Turnaround time.

t

xmturn

=(Flash_TURN_CYCLE + 1)*HCLK

0x8100007D

0xHHHHHHHH

Default 0x00000002

Table 8-2. SDRAM/Flash Controller Parameters (Continued)

Mnemonic

Hex Message