2 flash memory controller, 1 flash controller interface, 3 sdram/flash controller interface – Cirrus Logic CS4953xx User Manual

Page 80: 1 sdram/flash interface signals, 2 flash memory controller -2, 1 flash controller interface -2, 3 sdram/flash controller interface -2, 1 sdram/flash interface signals -2, Table 8-1. sdram interface signals -2

Flash Memory Controller

CS4953xx Hardware User’s Manual

DS732UM10

Copyright 2010 Cirrus Logic, Inc

8-2

8.2 Flash Memory Controller

The CS4953xx provides a glueless external Flash interface that supports connection to an external Flash

or EEPROM for code storage. This allows for products to be field-upgraded as new audio algorithms are

developed. The Flash controller allows autobooting to occur from a parallel Flash or EEPROM device.

Coefficients for filters may also be stored and recalled from parallel Flash or EEPROM.

8.2.1 Flash Controller Interface

The Flash controller allows the CS4953xx DSP to autoboot from a parallel Flash or EEPROM device.

Both Flash and EEPROM can be accessed using 8-bit, 16-bit, and 32-bit data modes (1-byte, 2-byte, and

4-byte words) and using an 8-bit or 16-bit data bus, where the word width is the number of bytes per

transfer, and the data bus size is the width of the physical interface to Flash. For example, an 8-bit data

bus setting uses only 8 data pins EXT_D[7:0] whereas the 16-bit data bus setting uses 16 data pins

(EXT_D[15:0]).

8.3 SDRAM/Flash Controller Interface

The physical interface of the SDRAM controller consists of 16 data pins (SD_DATA[15:0]), 13 address

pins (SD_ADDR[12:0]), 2 bank address pins (SD_BA[1:0]), and 9 control pins (SD_CS, SD_WE,

SD_DQM1, SD_DQM0, SD_CAS, SD_RAS, SD_CLKOUT, SD_CLKIN, SD_CLKEN). SD_CS is the

SDRAM chip select pin. The address and data pins are shared with the Flash interface. The CS4953xx

supports SDRAMs from 2 Mbytes to 64 Mbytes with various row, bank, and column configurations. The

size can be configured in the DynamicConfig0 register listed in

. Timing parameters of the

SDRAM port can be configured to meet various SDRAM requirements as described in

. The

default timing parameters have been chosen and tested to meet the requirements of Hynix

HY57V641620HG-H. By default, the SDRAM port is configured for 64 Mbits with 4 banks, 12 rows, and 8

columns with a RAS and CAS latency of 3.

The physical interface of the Flash controller consists of 16 data pins (EXT_D[15:0]), 20 address pins

(EXT_A[19:0]), and 4 control pins (EXT_CS1, EXT_CS2, EXT_OE, EXT_WE). The address and data pins

are shared with the SDRAM interface. EXT_CS1 is the Flash or EEPROM chip select pin. EXT_CS2 is

not supported. The Flash interface supports up to 1M x 8 addressable space (512k x 16 bits of Flash).

Data in Flash is stored big-endian, i.e. more significant bytes in a multi-byte word have lower addresses.

Note: When connected to a 16 Mbit SDRAM, the CS4953xx uses only SD_BA1 for bank selection.

8.3.1 SDRAM/Flash Interface Signals

shows the signal names, descriptions, and pin number of the signals associated with the

external SDRAM/Flash memory control port on the CS4953xx chip.

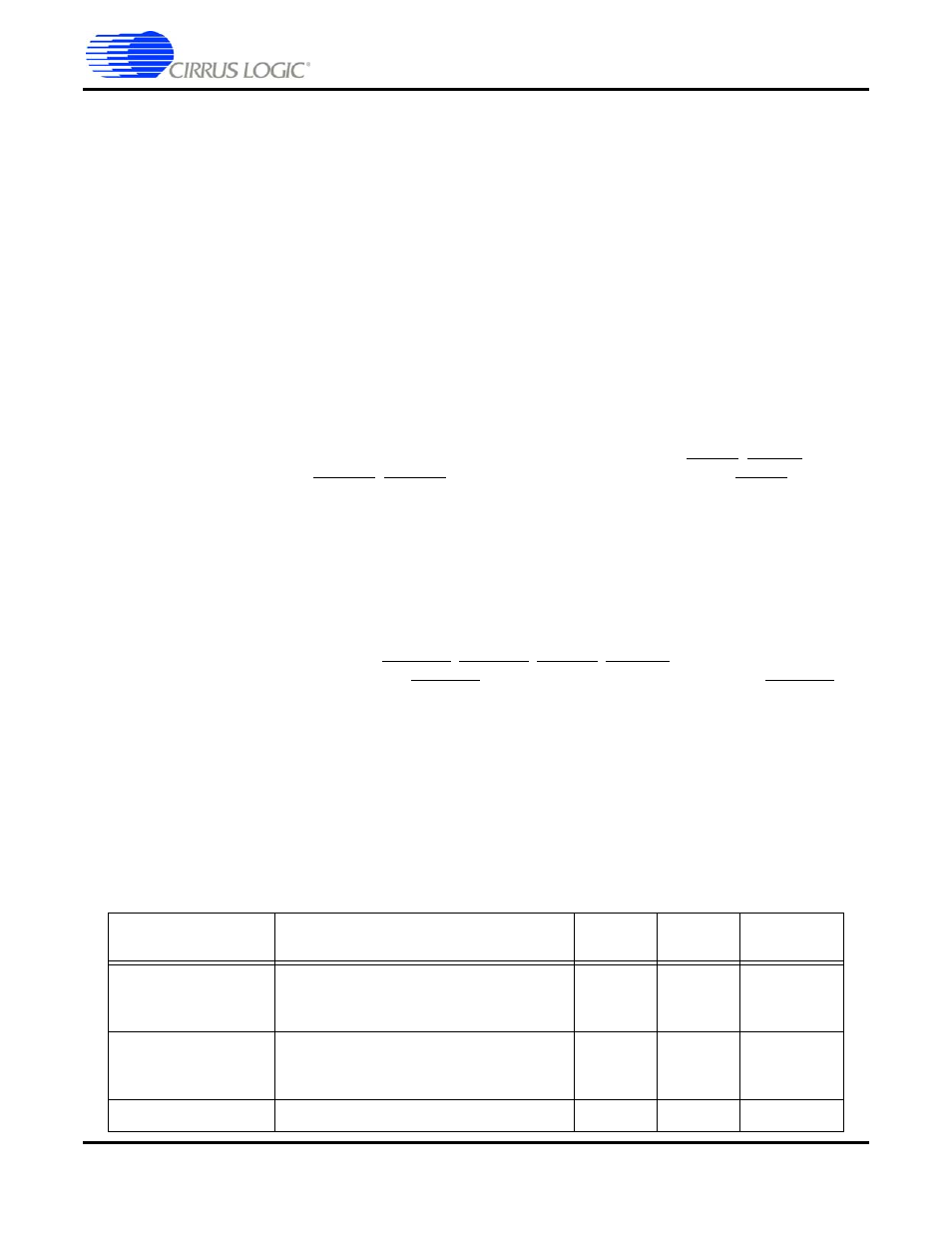

Table 8-1. SDRAM Interface Signals

Signal Name

Signal Description

LQFP-144

Pin #

LQFP-128

Pin #

Pin Type

SD_CLKOUT

SDRAM clock output. This output is tri-

stated when SDRAM interface is not

used.

51

80

Output

SD_CLKIN

SDRAM Clock input

Connects to trace from SDRAM device

CLKIN pin.

52

81

Input

SD_CLKEN

SDRAM Clock Enable Output

53

82

Output