3 host-controlled master boot from i2c rom, 4 host-controlled master boot from spi rom, 3 host-controlled master boot from i – Cirrus Logic CS4953xx User Manual

Page 25: 4 host-controlled master boot from spi rom -11, Table 2-4. hcmb_i2c message for the cs4953xx -11, Table 2-5. hcmb_spi message for cs4953xx -11, C rom

2-11

Copyright 2010 Cirrus Logic, Inc.

DS732UM10

Slave Boot Procedures

CS4953xx Hardware User’s Manual

HCMB_PARALLEL is used when the application code is stored in external parallel ROM, such as an

external 8-bit or 16-bit EEPROM or Flash. The external data bus width is specified by the ‘M’ variable in

the first control word. Also, the 20-bit start address is specified in the second control word with the ‘A’

variable. Read cycle parameters can also be configured by the ‘x’ and ‘y’ variables. The

HCMB_PARALLEL message should be substituted for the HCMB_

.

2.3.3.3 Host-Controlled Master Boot from I

2

C ROM

HCMB_I2C is used when the application code is stored in external I

2

C ROM, such as an I2C EEPROM.

The HCMB_I2C message should be substituted for the HCMB_

boot mode can be configured to interface with many types of I

2

C ROMs. The 16-bit start address is

specified by the ‘A’ variable. The I

2

C clock is derived from the internal core clock. This clock can be

divided down with the ‘c’ 12-bit divider variable. The command byte (the first byte to the I

2

C ROM) can be

defined by the ‘s’ variable. The CS4953xx control port used for the HCMB_I2C can be configured by the

‘p’ variable.

2.3.3.4 Host-Controlled Master Boot from SPI ROM

HCMB_SPI is used when the application code is stored in external SPI ROM, either SPI EEPROM or SPI

Flash. The HCMB_SPI message should be substituted for the HCMB_

.

This boot mode can be configured to interface with many types of SPI ROMs. The start address “A”

variable can be either 24-bit or 16-bit, configured by the “L” variable. Some SPI ROMs require some

‘dummy’ bytes after the address byte, before reading from the part, configurable by the ‘B’ variable.

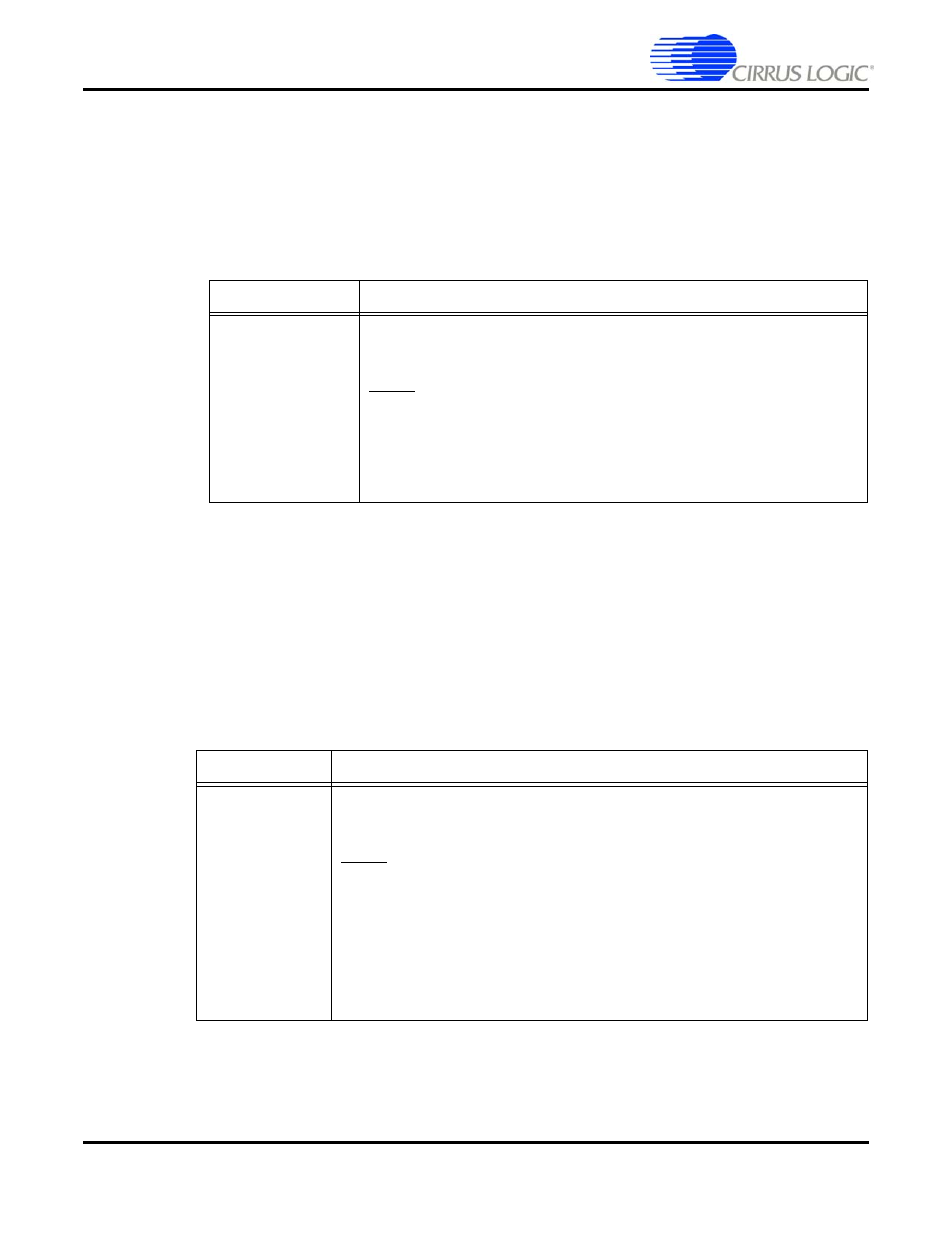

Table 2-4.

HCMB_I2C

message for the CS4953xx

MNEMONIC

VALUE

HCMB_I2C

1100 0000 000p cccc cccc cccc 0sss ssss

0000 0000 0000 0000 0000 0000 AAAA AAAA

Where

p = Serial Control Port Selection =1 for SCP2 (Normal Operation)

0 for SCP1 (Not Supported by O/S)

c = clock divider for I

2

C clock signal

s = 8-bit I

2

C command

A = 16-bit external memory start address

Table 2-5.

HCMB_SPI

message for CS4953xx

MNEMONIC

VALUE

HCMB_SPI

1101 BBB0 0SSp cccc cccc cccc ssss ssss

L000 0000 AAAA AAAA AAAA AAAA AAAA AAAA

Where

B = number of dummy bytes sent after Address, before read

S = Chip Select

p = Serial Control Port Selection =

1 for SCP2

0 for SCP1,

c = SPI clock speed = DSP Core Clock/(c+2)

s = 8-bit SPI command

L = Address Length = 0 for 16-bit Address, 1 for 24-bit Address

A = 24/16-bit external memory start address