3 performing a serial spi read, 3 performing a serial spi read -18, Figure 3-16. spi read flow diagram -18 – Cirrus Logic CS4953xx User Manual

Page 50

SPI Port

CS4953xx Hardware User’s Manual

DS732UM10

Copyright 2010 Cirrus Logic, Inc

3-18

5. The master should poll the SCP1_BSY signal until it goes high. If the SCP1_BSY signal is low, it

indicates that the CS4953xx is busy performing some task that requires halting the serial control port.

Once the CS4953xx is able to receive more data words, the SCP1_BSY signal will go high. Once the

SCP1_BSY signal is high, proceed to Step 3.

6. The master finishes the SPI write transaction by driving the CS4953xx SCP1_CS signal high.

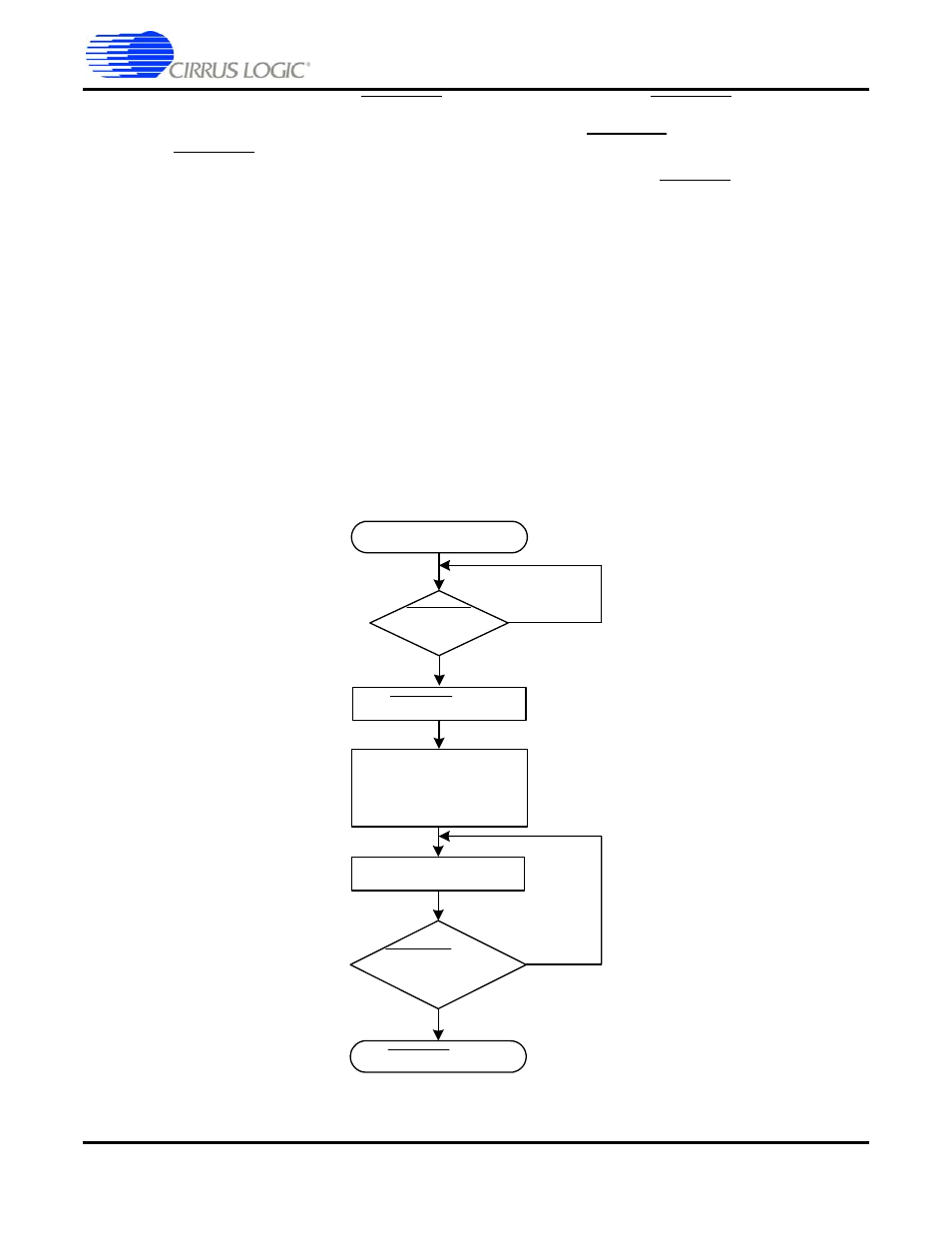

3.4.3.3 Performing a Serial SPI Read

Information provided in this section is intended as a functional description indicating how an external

device (Master) performs an SPI read from the CS4953xx (slave). The system designer must ensure that

all timing constraints of the SPI read cycle are met (see the CS4953xx datasheet for timing

specifications).

When performing a SPI read, the same protocol is used whether reading a single byte or multiple bytes.

From a hardware perspective, it makes no difference whether communication is a single byte or multiple

bytes of any message length, so long as the correct hardware protocol is followed. The example shown in

this section can be generalized to fit any SPI read situation.

The flow diagram shown in

, illustrates the sequence of events that define the SPI read

protocol. The Serial SPI read protocol is described in

.

Figure 3-16. SPI Read Flow Diagram

SCP1_IRQ

(LOW)?

SCP1_IRQ STILL

LOW?

SCP1_CS HIGH

Y

N

Y

N

START

SCP1_CS LOW

READ 4 DATA BYTES

WRITE ADDRESS BYTE

0x81