Table 8-2. sdram/flash controller parameters -5, Table 8-2 – Cirrus Logic CS4953xx User Manual

Page 83

8-5

Copyright 2010 Cirrus Logic, Inc.

DS732UM10

SDRAM/Flash Controller Interface

CS4953xx Hardware User’s Manual

Refer to External Memory Interface in the CS4953xx data sheet for timing parameters that are

summarized in

.

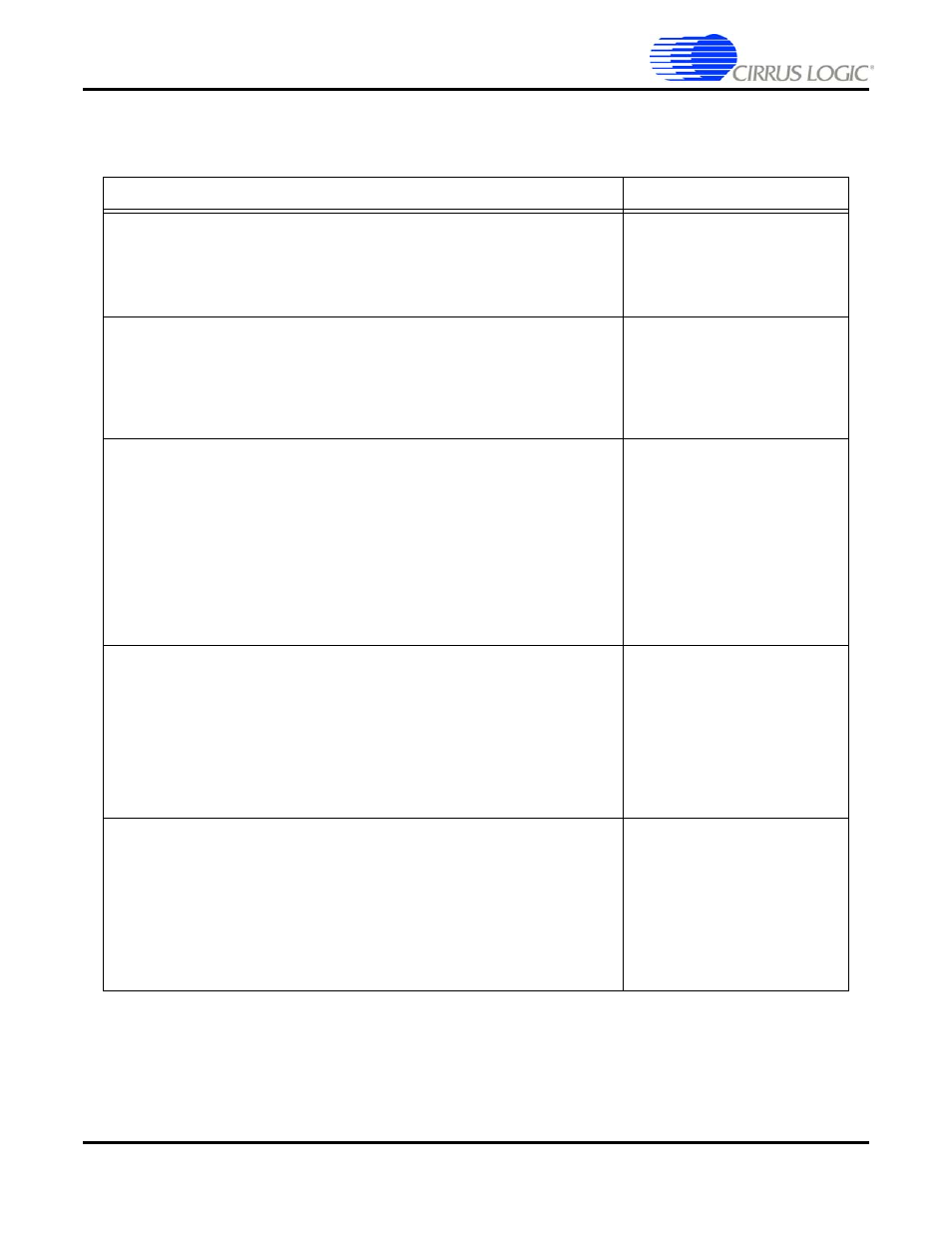

Table 8-2. SDRAM/Flash Controller Parameters

Mnemonic

Hex Message

Extmem_Setup_Control

Bit 31:5 = 0 = Reserved

Bit 4 = 0/1 = Disable/Enable Flash port

Bit 3:1 = 0 = Reserved

Bit 0 = 0/1 = Disable/Enable SDRAM port

0x8100005C

0xHHHHHHHH

Default: 0x00000011

CRUSConfig

Bit 31:9 = 0 = Reserved

Bit 8 = Pin Mapping, where:

0 = Enable Flash and SDRAM Mapping

1 = Enable Flash and SRAM Mapping

Bit 7:0 = 0 = Reserved

0x8100005D

0xHHHHHHHH

Default: 0x00000000

DynamicRefresh

Configure the refresh period

Bit 31:11 = 0 = Reserved

Bit 10:0 = REFRESH, where:

0x0 = refresh disabled.

0x1 = 1x16 = 16 HCLK ticks between refresh cycles

0x8 = 8x16 = 128 HCLK ticks between refresh cycles

0x1 to 0x7FF = REFRESH*16 HCLK ticks between refresh cycles

Example:

Refresh Period = 15.625

μ

S, HCLK = 120Mhz

REFRESH = (15.625

μ

S*120Mhz)/16 = 117 = 0x75

0x81000061

0xHHHHHHHH

Default 0x00000075

DynamictRP

Configure the precharge command period

Bit 31:4 = 0 = Reserved

Bit 3:0 = Trp, where:

0x0 to 0xE = (n + 1) DSP clk cycles.

0xF = 16 DSP clk cycles.

Example:

Trp = 20nS, HCLK = 120Mhz

Trp =20nS*120Mhz - 1 = 1.4 = 0x2

0x81000062

0xHHHHHHHH

Default 0x00000002

DynamictRAS

Configure the active to precharge command period

Bit 31:4 = 0 = Reserved

Bit 3:0 = Tras, where:

0x0 to 0xE = (n + 1) DSP clk cycles.

0xF = 16 DSP clk cycles.

Example:

Tras = 45nS, HCLK = 120Mhz

Tras =45nS*120Mhz - 1 = 3.8 = 0x4

0x81000063

0xHHHHHHHH

Default 0x00000004