Figure 3-10. sample waveform for i, Figure 3-11. sample waveform for i – Cirrus Logic CS4953xx User Manual

Page 44

D

S

73

2U

M

1

0

C

op

yri

ght 201

0

C

irr

us Log

ic

,

In

c

3

-1

2

I2

C

P

o

rt

C

S

495

3xx

H

a

rd

w

a

re

U

s

e

r’s

M

a

n

ual

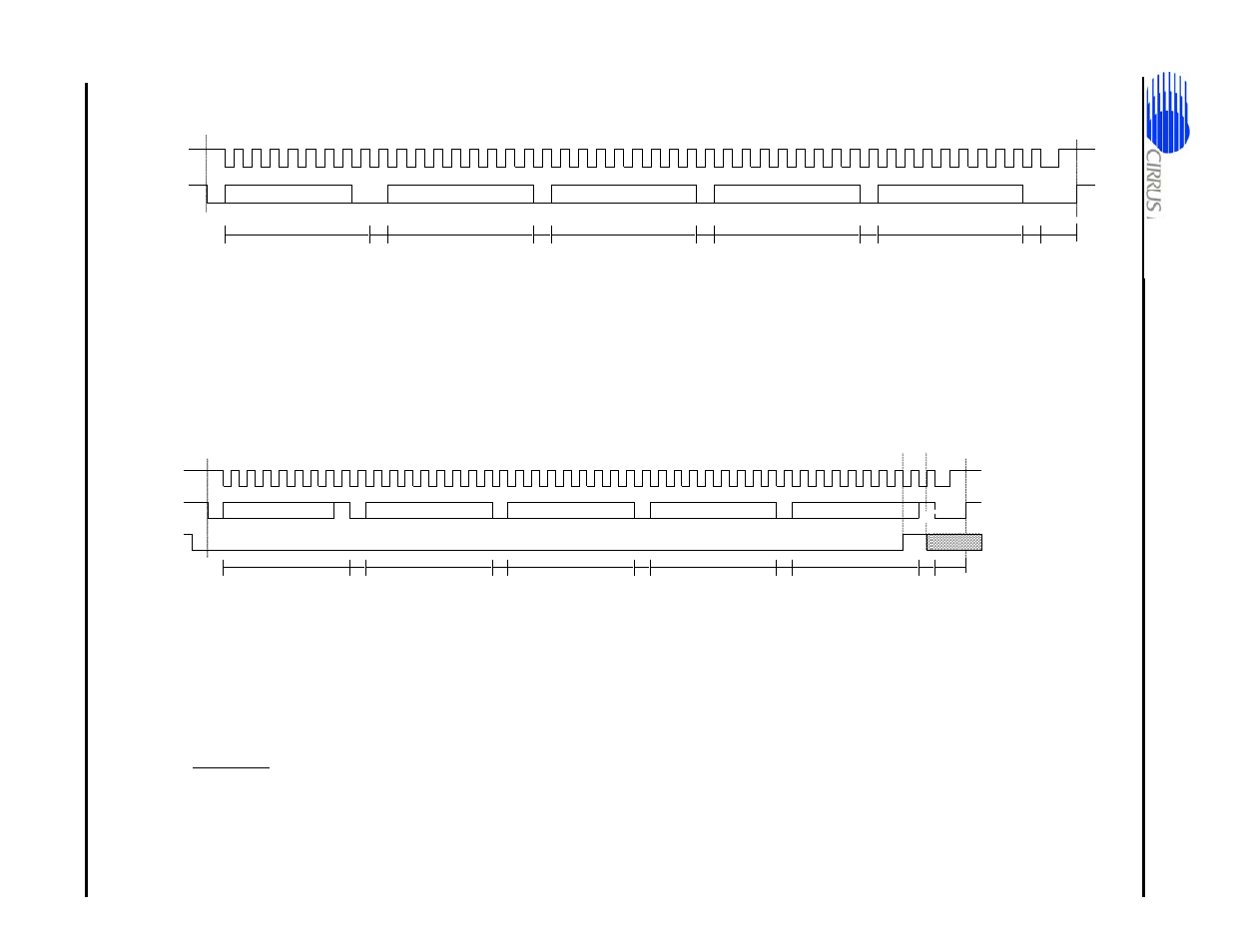

Figure 3-10. Sample Waveform for I

2

C Write Functional TIming

Note: The I

2

C slave is always responsible for driving the ACK for the address byte.

Figure 3-11. Sample Waveform for I

2

C Read Functional TIming

Notes:

1.

The I

2

C slave is drives the ACK for the address byte.

2. The I

2

C master is responsible for controlling ACK during I

2

C reads. In general, the receiver in an I

2

C transaction is responsible for

providing ACK.

3. SCP1_IRQ remains low until the rising edge of the clock for the last bit of the last byte read from the I

2

C slave.

4. A NACK is sent by the master after the last byte to indicate the end of the read cycle. This must be followed with an I

2

C Stop condition or

I

2

C Repeated-Start condition.

5. If there are more data words to read, IRQ will fall at the rising edge of CLK for the NACK. Otherwise, IRQ remains high until an I

2

C Stop

condition or an I

2

C Repeated-Start condition occurs.

Start

SCP1_CLK

SCP1_SDA

Data Byte 3 (MSB)

Stop

7-bit Address

R/

W

ACK

AC

K

Data Byte 2

AC

K

Data Byte 1

ACK

Data Byte 0 (LSB)

ACK

M

S

M

S

M

S

M

S

M

S

M

Notes: 1.

The

I

2

C slave is always responsible for driving the ACK for the address byte.

2. The I

2

C slave is responsible for driving the ACK during I

2

C writes.

Start

SCP1_CLK

SCP1_SDA

Data Byte 3 (MSB)

Stop

7-bit Address

R/

W

AC

K

AC

K

Data Byte 2

AC

K

Data Byte 1

AC

K

Data Byte 0 (LSB)

SCP1_IRQ#

N

ACK

M

S

S

M

S

M

S

M

S

M

M

M = Master Drives SDA

S = Slave Drives SDA