Figure 3-2. block diagram of i, Table 3-1. serial control port 1 i – Cirrus Logic CS4953xx User Manual

Page 35

3-3

Copyright 2010 Cirrus Logic, Inc.

DS732UM10

I2C Port

CS4953xx Hardware User’s Manual

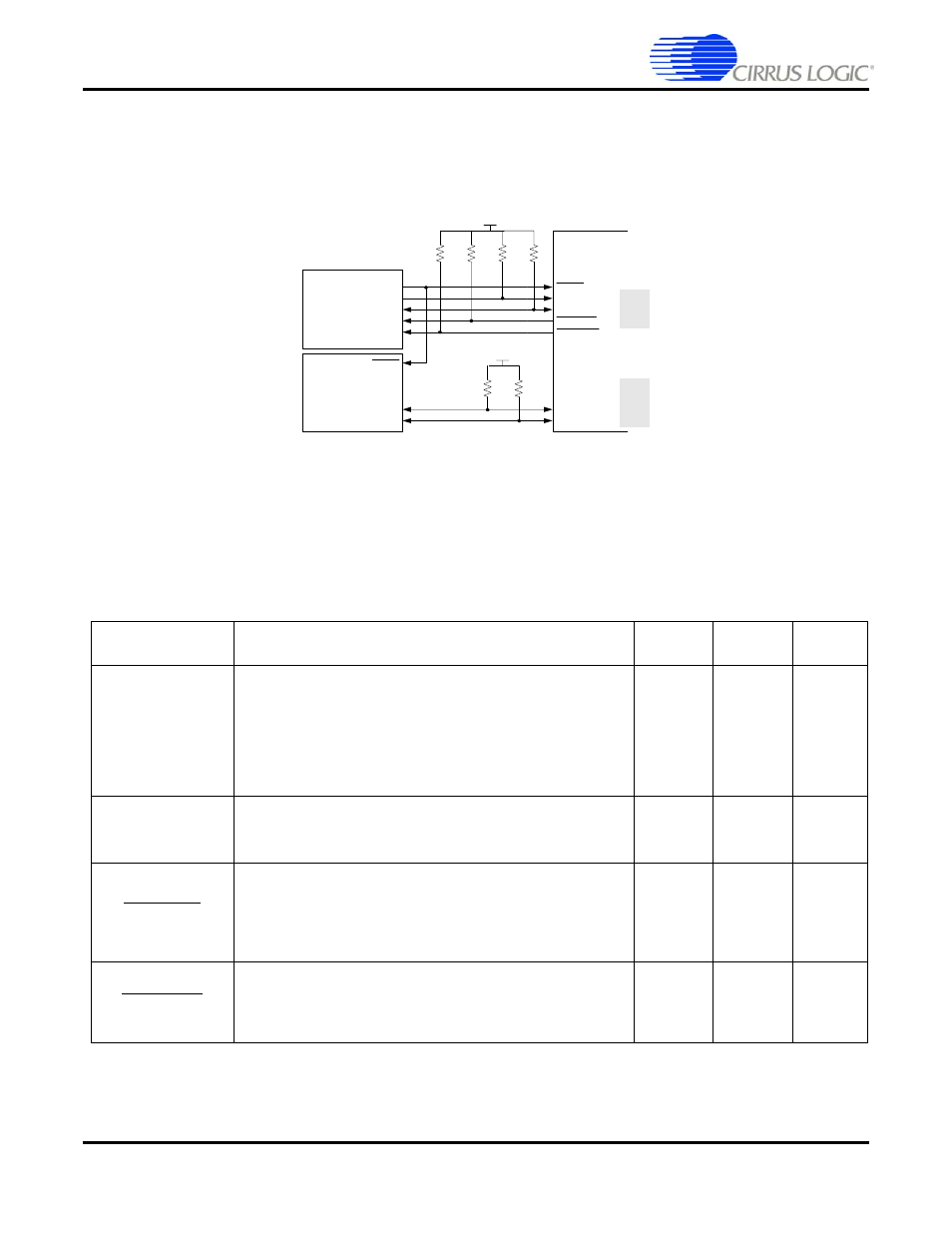

, two serial ports are available on the CS4953xx. Each can be configured as either

master or slave. For Audio applications, SCP1 is configured as a slave port and SCP2 is configured as a

master port. SCP2 is used only in systems that are booting from serial EEPROM.

Figure 3-2. Block Diagram of I

2

C System Bus

shows the signal names, descriptions, and pin number of the signals associated with the I

2

C

Serial Control Port on the CS4953xx.

Table 3-1. Serial Control Port 1 I

2

C Signals

Pin Name

Pin Description

LQFP-144

Pin #

LQFP-128

Pin #

Pin

Type

SCP1_CLK

I

2

C Control Port Bit Clock.

In master mode, this pin serves as the serial control clock

output (open drain in I

2

C mode / output in SPI mode). In

serial slave mode, this pin serves as the serial control

clock input. In I

2

C slave mode the clock can be pulled low

by the port to stall the master.

99

126

Open

Drain

SCP1_SDA

Bidirectional Data I

2

C Mode Master/Slave Data IO. In I

2

C

master and slave mode, this open drain pin serves as the

data input and output.

97

124

Open

Drain

SCP1_IRQ

Control Port Data Ready Interrupt Request, Output,

Active Low

This pin is driven low when the DSP has a message for

the host to read. The pin will go high when the host has

read the message and the DSP has no further messages.

100

4

Open

Drain

SCP1_BSY

Serial Control Port 1 Input Busy, Output, Active Low

This pin is driven low when the control port’s receive

buffer is full. Internal Buffer is 4 bytes (1 DSP Word)

deep.

102

128

Open

Drain

System Microcontroller

R ESET

SCP1_CLK

SCP1_SDA

SCP1_IR Q

SCP1_BSY

CS4953xx

3.3k

3.3k

3.3V

3.3k

3.3k

EEPRO M

RESET

Serial Clock

Serial Data

SCP2_CLK

SCP2_SDA

3.3k

3.3k

3.3V

SL

AV

E

ONL

Y

MA

S

T

E

R

ON

L

Y