2 operational mode selection, 2 operational mode selection -3, Table 2-1. operation modes -3 – Cirrus Logic CS4953xx User Manual

Page 17

2-3

Copyright 2010 Cirrus Logic, Inc.

DS732UM10

Operational Mode Selection

CS4953xx Hardware User’s Manual

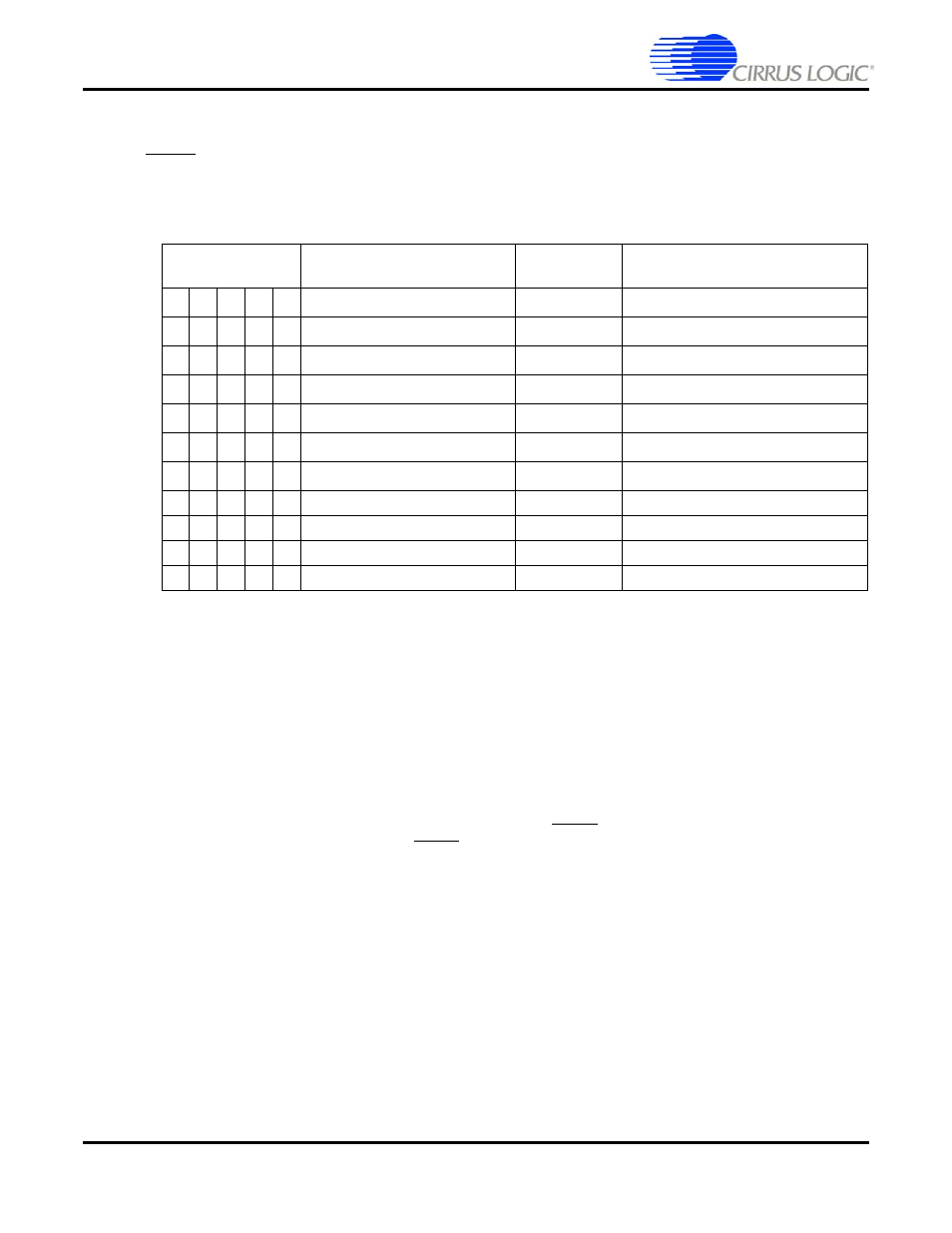

2.2 Operational Mode Selection

The operational mode for the CS4953xx is selected by the values of the HS[4:0] pins on the rising edge of

RESET. This value determines the communication mode used until the part is reset again. This value also

determines the method for loading application code. The table below shows the different operational

modes and the HS[4:0] values for each mode.

1. In I

2

C master mode, the Image Start address (0x0) is sent as a 16-bit value, with the default I

2

C address of

0x50, I

2

C clock frequency = F

dclk

/ 72.

2. SPI master mode 1 is to support the legacy 16-bit SPI EEPROM. The following defaults are used: SPI

Command Byte 0x03, Image Start address 0x0 is sent as a 16-bit value, no dummy bytes, SPI clock

frequency = F

dclk

/ 4.

3. In SPI Master mode 2, the following defaults are used: SPI Command Byte 0x68, Image Start address 0x0 is

sent as a 24-bit value, 4 dummy bytes sent following the address (and before reading image data), SPI clock

frequency = F

dclk

/ 2. This mode supports the Atmel SPI Flash memory.

4. In SPI Master mode 3, the following defaults are used: SPI command byte 0x03, Image Start address 0x0 is

sent as a 24-bit value, no dummy bytes, SPI clock frequency = F

dclk

/ 2. This mode supports the ST SPI

EEPROM devices.

5. For all SPI Master boot modes, by default GPIO20 is used as EE_CS, but the HCMB message can be

configured to select an alternate pin for EE_CS.

6. For Flash Master modes, the following defaults are used: clock ratio=1:1, Endian Mode = little-endian, Chip

Select polarity = active-low, 0-cycle delay from CS/Address Change to Output Enable, 4-cycle delay from CS

to Read Access.

7. Master Boot Modes are currently not supported by the O/S.

8. F

dclk

is specified in the CS4953xx data sheet.

Table 2-1. Operation Modes

HS[4:0]

Mode

Boot Master

Device

Boot Slave Device

X

0

0

0

0

Master SCP1 I

2

C

CS4953xx

I

2

C External ROM

1,8

X

1

0

0

0

Master SCP1 SPI1

CS4953xx

SPI (Mode 1) External ROM

2, 5, 7, 8

X

0

0

0

1

Master SCP1 SPI2

CS4953xx

SPI (Mode 2) External ROM

3, 5, 7, 8

X

1

0

0

1

Master SCP1 SPI3

CS4953xx

SPI (Mode 3) External ROM

4, 5, 7, 8

X

0

0

1

0

Master 8-bit Flash

CS4953xx

8-bit External ROM

6

X

1

0

1

0

Master 16-bit Flash

CS4953xx

16-bit External ROM

6

X

X

1

0

0

Slave/HCMB SCP1 I

2

C

System Host

CS4953xx

X

X

1

0

1

Slave/HCMB SCP1 SPI

System Host

CS4953xx

X

X

1

1

0

Slave/HCMB PCP Intel

System Host

CS4953xx

X

X

1

1

1

Slave/HCMB PCP Motorola

System Host

CS4953xx

X

X

0

1

1

Slave/HCMB PCP Mux

System Host

CS4953xx