Cirrus Logic CS4953xx User Manual

Page 85

8-7

Copyright 2010 Cirrus Logic, Inc.

DS732UM10

SDRAM/Flash Controller Interface

CS4953xx Hardware User’s Manual

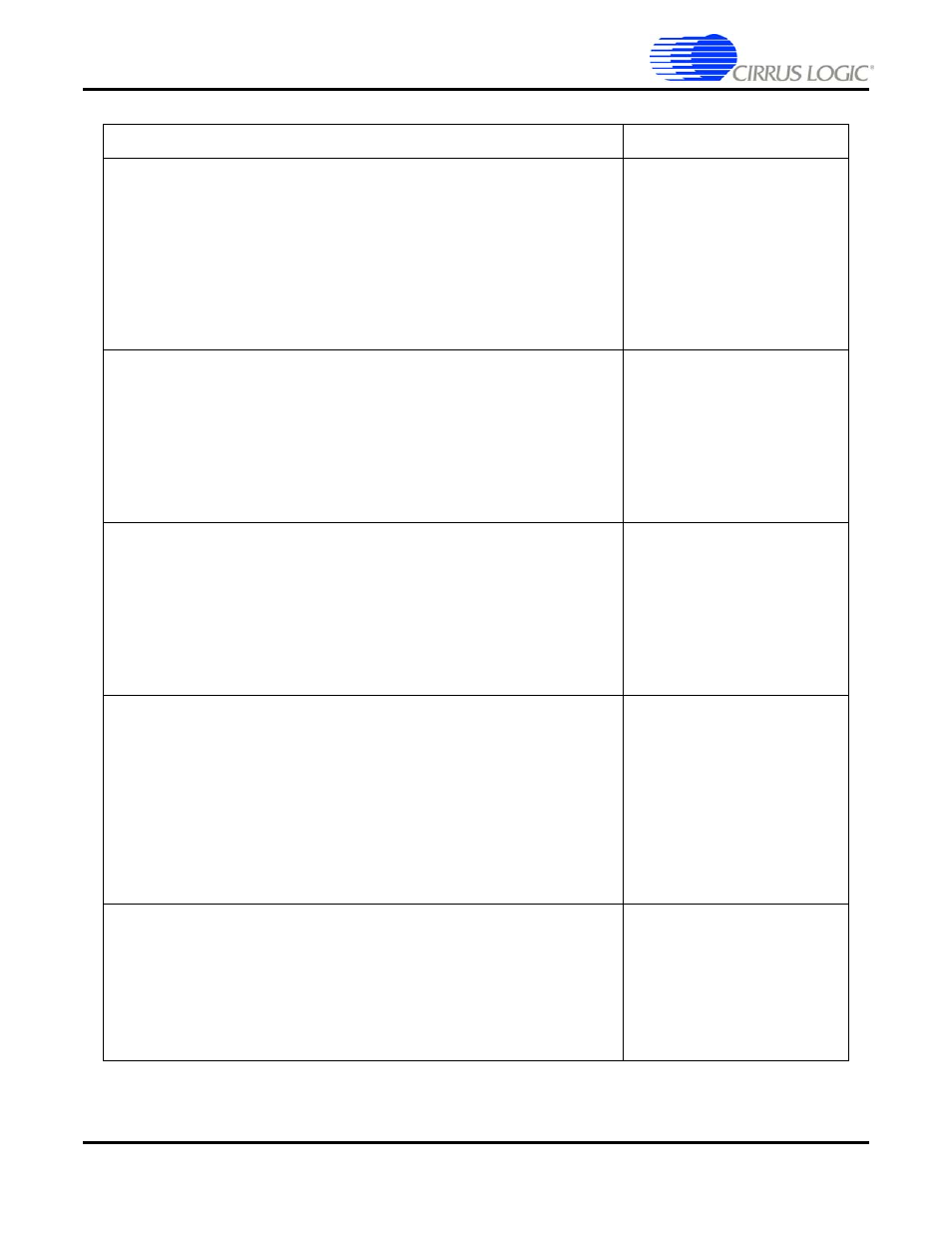

DynamictRFC

Configure the auto refresh period and auto refresh to active command

time. Also known as Trrc

Bit 31:5 = 0 = Reserved

Bit 4:0 = Trc, where:

0x0 to 0xE = (n + 1) DSP clk cycles.

0x1F = 32 DSP clk cycles.

Example:

Trc = 65 nS, HCLK = 120Mhz

Trc = 65 nS * 120 Mhz -1=7.8-1 = 0x7

0x81000069

0xHHHHHHHH

Default 0x00000007

DynamictXSR

Configure the exit self refresh to active command time.

Bit 31:5 = 0 = Reserved

Bit 4:0 = Txsr, where:

0x0 to 0x1E = (n + 1) DSP clk cycles.

0x1F = 32DSP clk cycles.

Example:

Txsr = 83 nS, HCLK = 120Mhz

Txsr = 83 nS * 120 Mhz-1 =10-1 = 0x9

0x8100006A

0xHHHHHHHH

Default 0x00000009

DynamictRRD

Configure the active bank A to active bank B latency

Bit 31:4 = 0 = Reserved

Bit 3:0 = Trrd, where:

0x0 to 0xE = (n + 1) DSP clk cycles.

0xF= 16 DSP clk cycles.

Example:

Trrd = 15 nS, HCLK = 120Mhz

Trrd = 15 nS * 120 Mhz - 1= 1.8 - 1 = 0x1

0x8100006B

0xHHHHHHHH

Default 0x00000001

DynamictMRD

Configure the load mode register to active command time. Also known as

Trsa

Bit 31:4 = 0 = Reserved

Bit 3:0 = Tmrd, where:

0x0 to 0xE = (n + 1) DSP clk cycles.

0xF= 16 DSP clk cycles.

Example:

Tmrd = 1CLKs, HCLK = 120Mhz

Tmrd = 1-1 = 0x0

0x8100006C

0xHHHHHHHH

Default 0x00000000

DynamicConfig0

Configure the active bank A to active bank B latency

Bit 31:12 = 0 = Reserved

Bit 11:7 = External bus address mapping (Row, Bank, Column),where:

00001 = 16Mb (1Mx16), 2 banks, row length = 11, column length = 8

00101 = 64Mb (4Mx16), 4 banks, row length = 12, column length = 8

01001 = 128Mb (8Mx16), 4 banks, row length = 12, column length = 9

Bit 6:0 = 0 = Reserved

0x8100006E

0xHHHHHHHH

Default 0x00000280

Table 8-2. SDRAM/Flash Controller Parameters (Continued)

Mnemonic

Hex Message