Rainbow Electronics DS2151Q User Manual

Page 6

DS2151Q

022697 6/46

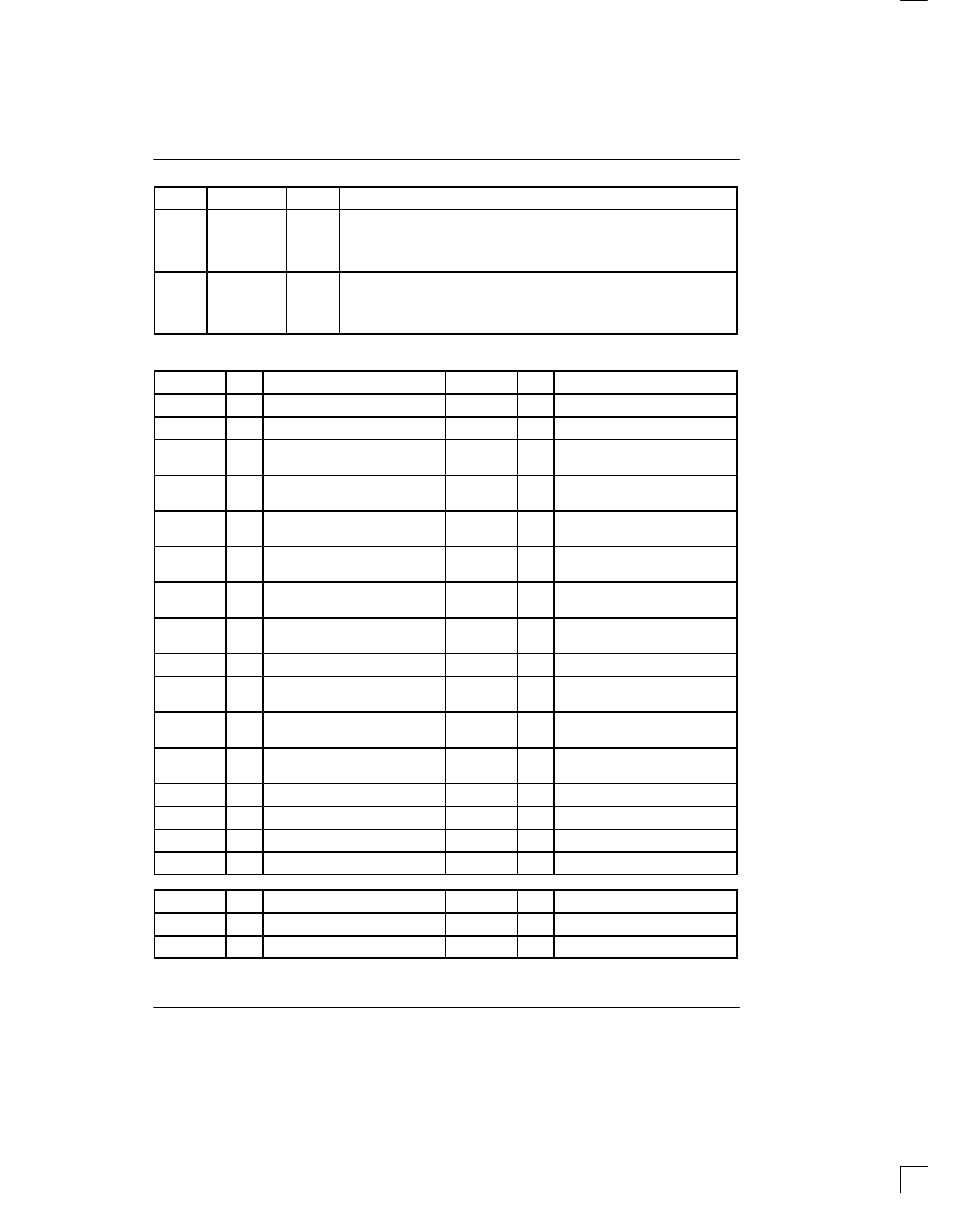

PIN

DESCRIPTION

TYPE

SYMBOL

40

TCHCLK

O

Transmit Channel Clock. 192 KHz clock which pulses high during the LSB

of each channel. Useful for parallel to serial conversion of channel data,

locating Robbed–Bit signaling bits, and for blocking clocks in DDS applica-

tions. See Section 13 for timing details.

41

42

43

44

AD0

AD1

AD2

AD3

I/O

Address/Data Bus. A 8–bit multiplexed address/data bus.

DS2151Q REGISTER MAP

ADDRESS

R/W

REGISTER NAME

ADDRESS

R/W

REGISTER NAME

20

R/W

Status Register 1.

30

R/W

Common Control Register 3.

21

R/W

Status Register 2.

31

R/W

Receive Information Register 2.

22

R/W

Receive Information Register 1.

32

R/W

Transmit Channel Blocking Reg-

ister 1.

23

R

Line code Violation Count Regis-

ter 1.

33

R/W

Transmit Channel Blocking Reg-

ister 2.

24

R

Line code Violation Count Regis-

ter 2.

34

R/W

Transmit Channel Blocking Reg-

ister 3.

25

R

Path Code Violation Count Reg-

ister 1. (1)

35

R/W

Transmit Control Register 1.

26

R

Path Code Violation Count Reg-

ister 2.

36

R/W

Transmit Control Register 2.

27

R

Multiframe Out of Sync Count

Register 2.

37

R/W

Common Control Register 1.

28

R

Receive FDL Register

38

R/W

Common Control Register 2.

29

R/W

Receive FDL Match Register 1.

39

R/W

Transmit Transparency Register

1.

2A

R/W

Receive FDL Match Register 2.

3A

R/W

Transmit Transparency Register

2.

2B

R/W

Receive Control Register 1.

3B

R/W

Transmit Transparency Register

3.

2C

R/W

Receive Control Register 2.

3C

R/W

Transmit Idle Register 1.

2D

R/W

Receive Mark Register 1.

3D

R/W

Transmit Idle Register 2.

2E

R/W

Receive Mark Register 2.

3E

R/W

Transmit Idle Register 3.

2F

R/W

Receive Mark Register 3.

3F

R/W

Transmit Idle Definition Register.

60

R

Receive Signaling Register 1.

70

R/W

Transmit Signaling Register 1.

61

R

Receive Signaling Register 2.

71

R/W

Transmit Signaling Register 2.

62

R

Receive Signaling Register 3.

72

R/W

Transmit Signaling Register 3.