Rainbow Electronics DS2151Q User Manual

Page 14

DS2151Q

022697 14/46

When the CCR3.3 is set to one, the DS2151Q will force

the transmitted stream to meet this requirement no mat-

ter the content of the transmitted stream. When running

B8ZS, the CCR3.3 bit should be set to zero since B8ZS

encoded data streams cannot violate the pulse density

requirements.

POWER–UP SEQUENCE

On power–up, after the supplies are stable, the

DS2151Q should be configured for operation by writing

to all of the internal registers (this includes setting the

Test Register to 00Hex) since the contents of the inter-

nal registers cannot be predicted on power–up. Next,

the LIRST bit should be toggled from zero to one to reset

the line interface (it will take the DS2151Q about 40ms

to recover from the LIRST being toggled). Finally, after

the SYSCLK input is stable, the ESR bit should be

toggled from a zero to a one (this step can be skipped if

the elastic stores are disabled).

4.0 STATUS AND INFORMATION

REGISTERS

There is a set of four registers that contain information

on the current real time status of the DS2151Q, Status

Register 1 (SR1), Status Register 2 (SR2), Receive

Information Register 1 (RIR1), and Receive Information

Register 2 (RIR2). When a particular event has

occurred (or is occurring), the appropriate bit in one of

these four registers will be set to a one. All of the bits in

these registers operate in a latched fashion. This

means that if an event occurs and a bit is set to a one in

any of the registers, it will remain set until the user reads

that bit. The bit will be cleared when it is read and it will

not be set again until the event has occurred again or if

the alarm(s) is still present.

The user will always precede a read of these registers

with a write. The byte written to the register will inform

the DS2151Q which bits the user wishes to read and

have cleared. The user will write a byte to one of these

four registers, with a one in the bit positions he or she

wishes to read and a zero in the bit positions he or she

does not wish to obtain the latest information on. When

a one is written to a bit location, the read register will be

updated with current value and the previous value will

be cleared. When a zero is written to a bit position, the

read register will not be updated and the previous value

will be held. A write to the status and information regis-

ters will be immediately followed by a read of the same

register. The read result should be logically AND’ed

with the mask byte that was just written and this value

should be written back into the same register to insure

that the bit does indeed clear. This second write is nec-

essary because the alarms and events in the status reg-

isters occur asynchronously in respect to their access

via the parallel port. The write–read–write scheme is

unique to the four status registers and it allows an exter-

nal microcontroller or microprocessor to individually poll

certain bits without disturbing the other bits in the regis-

ter. This operation is key in controlling the DS2151Q

with higher–order software languages.

The SR1 and SR2 registers have the unique ability to

initiate a hardware interrupt via the INT1 and INT2 pins

respectively. Each of the alarms and events in the SR1

and SR2 can be either masked or unmasked from the

interrupt pins via the Interrupt Mask Register 1 (IMR1)

and Interrupt Mask Register 2 (IMR2) respectively.

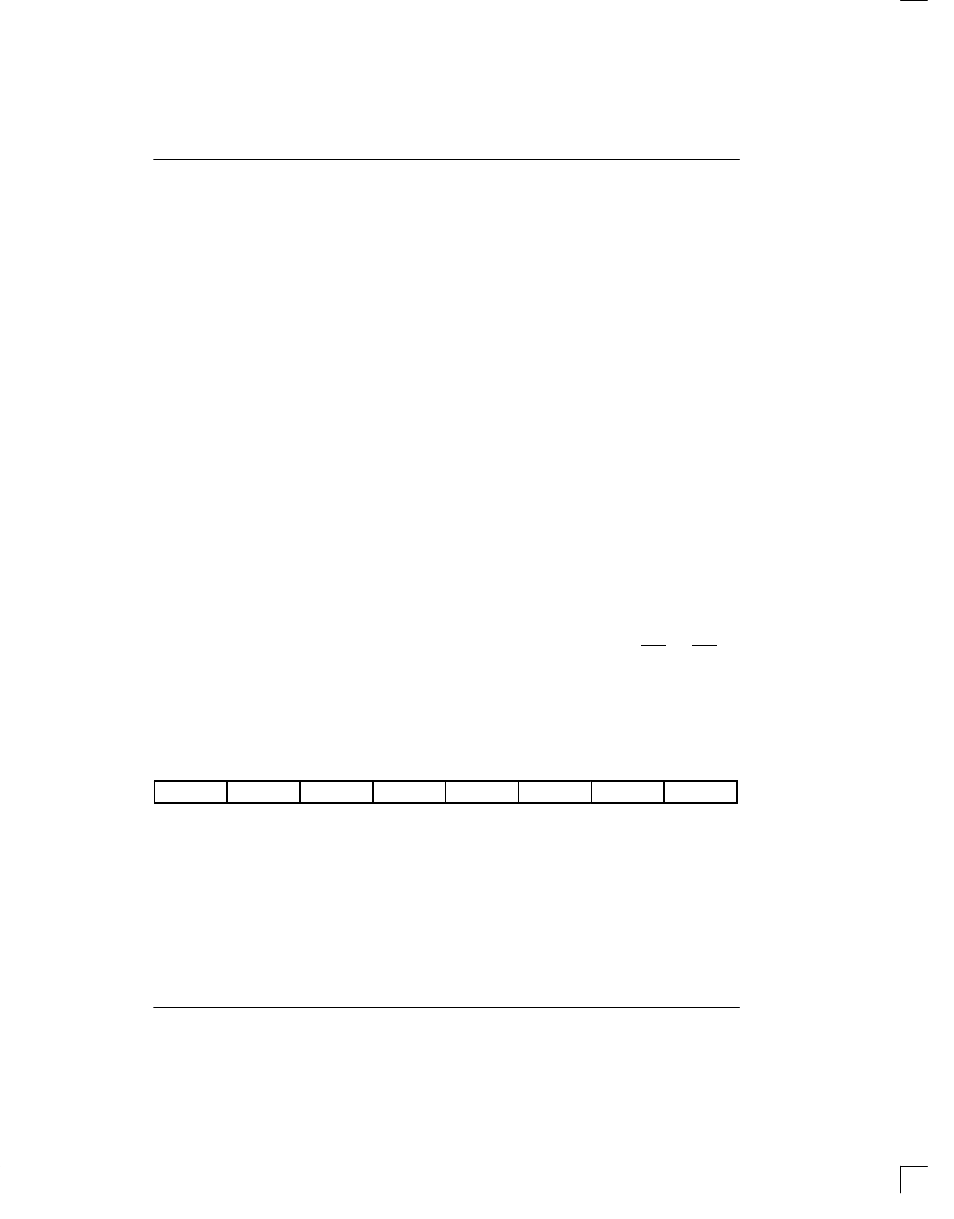

RIR1: RECEIVE INFORMATION REGISTER 1 (Address=22 Hex)

(MSB)

(LSB)

COFA

8ZD

16ZD

RESF

RESE

SEFE

B8ZS

FBE

SYMBOL

POSITION

NAME AND DESCRIPTION

COFA

RIR1.7

Change of Frame Alignment. Set when the last resync resulted in a

change of frame or multiframe alignment.

8ZD

RIR1.6

Eight Zero Detect. Set when a string of eight consecutive zeros have been

received at RPOS and RNEG.

16ZD

RIR1.5

Sixteen Zero Detect. Set when a string of sixteen consecutive zeros have

been received at RPOS and RNEG.

RESF

RIR1.4

Receive Elastic Store Full. Set when the receive elastic store buffer fills

and a frame is deleted.