Rainbow Electronics DS2151Q User Manual

Page 12

DS2151Q

022697 12/46

DS2151Q. When PLB is enabled, the following will

occur:

1. data will be transmitted from the TTIP and TRING

pins synchronous with RCLK instead of TCLK

2. all of the receive side signals will continue to operate

normally

3. the TCHCLK and TCHBLK signals are forced low

4. data at the TSER pin is ignored

5. the TLCLK signal will become synchronous with

RCLK instead of TCLK.

FRAMER LOOPBACK

When CCR1.0 is set to a one, the DS2151Q will enter a

Framer LoopBack (FLB) mode. This loopback is useful

in testing and debugging applications. In FLB, the

DS2151Q will loop data from the transmit side back to

the receive side. When FLB is enabled, the following

will occur:

1. unless the RLB is active, an unframed all one’s code

will be transmitted at TTIP and TRING

2. data off the T1 line at RTIP and RRING will be

ignored

3. the RCLK output will be replaced with the TCLK

input.

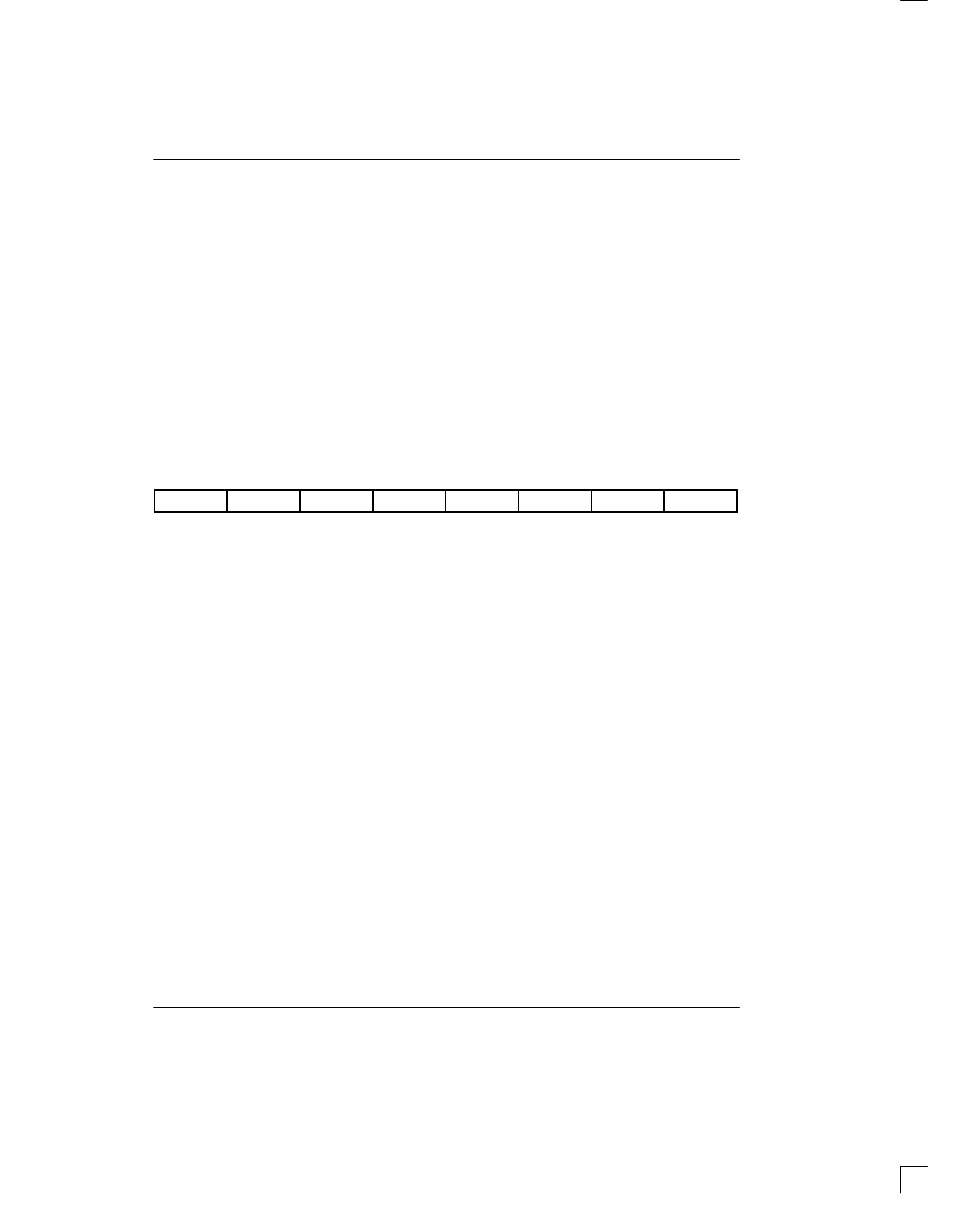

CCR2: COMMON CONTROL REGISTER 2 (Address=38 Hex)

(MSB)

(LSB)

TFM

TB8ZS

TSLC96

TFDL

RFM

RB8ZS

RSLC96

RFDL

SYMBOL

POSITION

NAME AND DESCRIPTION

TFM

CCR2.7

Transmit Frame Mode Select.

0=D4 framing mode

1=ESF framing mode

TB8ZS

CCR2.6

Transmit B8ZS Enable.

0=B8ZS disabled

1=B8ZS enabled

TSLC96

CCR2.5

Transmit SLC–96/Fs Bit Insertion Enable.

0=SLC–96 disabled

1=SLC–96 enabled

TFDL

CCR2.4

Transmit Zero Stuffer Enable.

0=zero stuffer disabled

1=zero stuffer enabled

RFM

CCR2.3

Receive Frame Mode Select.

0=D4 framing mode

1=ESF framing mode

RB8ZS

CCR2.2

Receive B8ZS Enable.

0=B8ZS disabled

1=B8ZS enabled

RSLC96

CCR2.1

Receive SLC–96 Enable.

0=SLC–96 disabled

1=SLC–96 enabled

RFDL

CCR2.0

Receive Zero Destuffer Enable.

0=zero destuffer disabled

1=zero destuffer enabled