Rainbow Electronics DS2151Q User Manual

Page 33

DS2151Q

022697 33/46

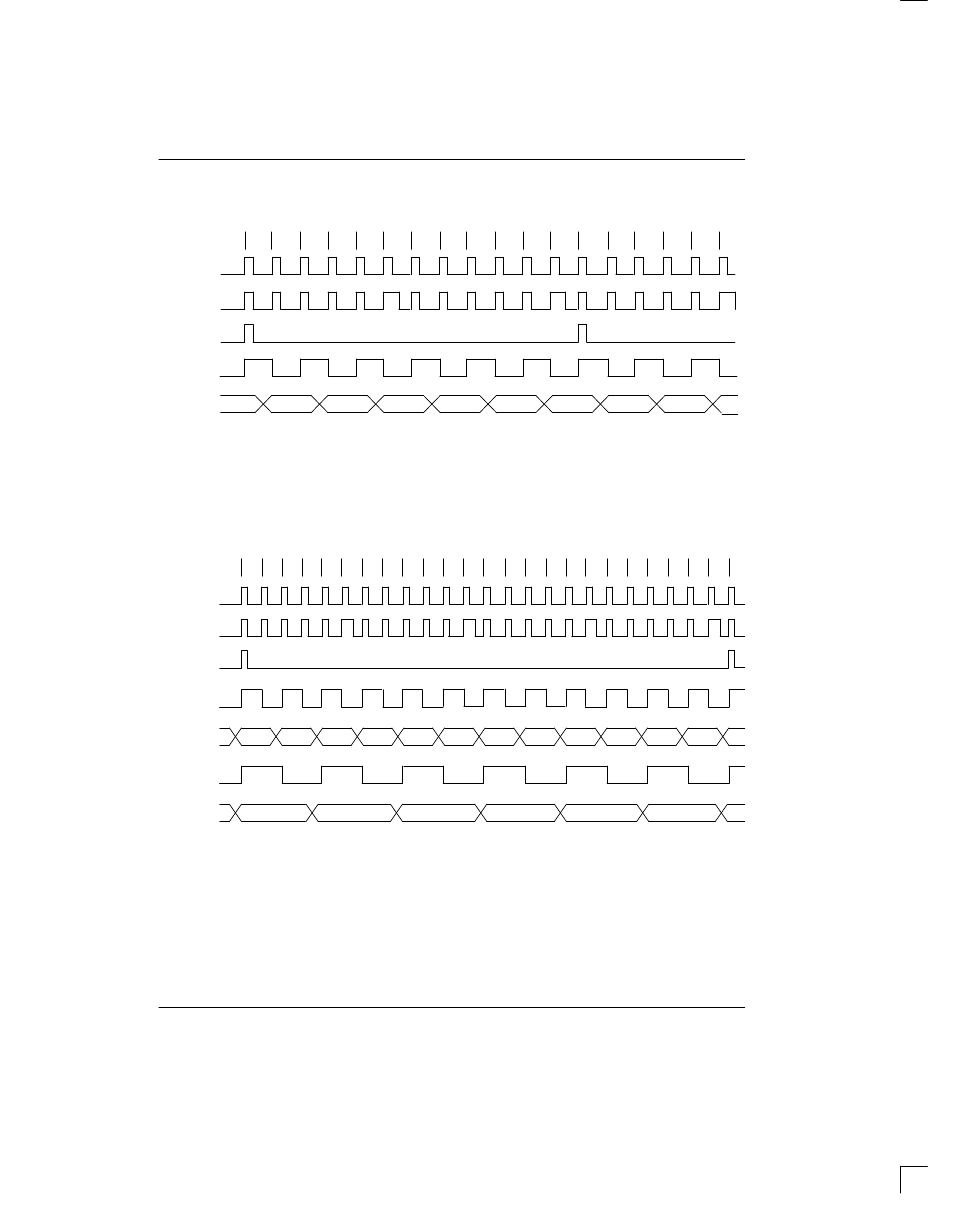

13.0 TIMING DIAGRAMS

RECEIVE SIDE D4 TIMING Figure 13–1

1

2

3

4

5

6

7

8

9

10

11

12

1

2

3

4

5

FRAME#

RSYNC

1

RSYNC

2

RSYNC

3

RLCLK

RLINK

4

NOTES:

1. RSYNC in the frame mode (RCR2.4=0) and double-wide frame sync is not enabled (RCR2.5=0).

2. RSYNC in the frame mode (RCR2.4=0) and double-wide frame sync is enabled (RCR2.5=1).

3. RSYNC in the multiframe mode (RCR2.4=1).

4. RLINK data (S–bit) is updated one bit prior to even frames and held for two frames.

RECEIVE SIDE ESF TIMING Figure 13–2

1

2

3

4

5

6

7

8

9

10

11 12

13

14

15 16 17

FRAME#

RSYNC

1

RSYNC

2

RSYNC

3

RLCLK

4

RLINK

5

RLCLK

6

RLINK

7

18

19

20 21 22 23

24

NOTES:

1. RSYNC in the frame mode (RCR2.4=0) and double-wide frame sync is not enabled (RCR2.5=0).

2. RSYNC in the frame mode (RCR2.4=0) and double-wide frame sync is enabled (RCR2.5=1).

3. RSYNC in the multiframe mode (RCR2.4=1).

4. ZBTSI mode disabled (RCR2.6=0).

5. RLINK data (FDL bits) is updated one bit time before odd frames and held for two frames.

6. ZBTSI mode is enabled (RCR2.6=1).

7. RLINK data (Z bits) is updated one bit time before odd frame and held for four frames.