Rainbow Electronics DS2151Q User Manual

Page 13

DS2151Q

022697 13/46

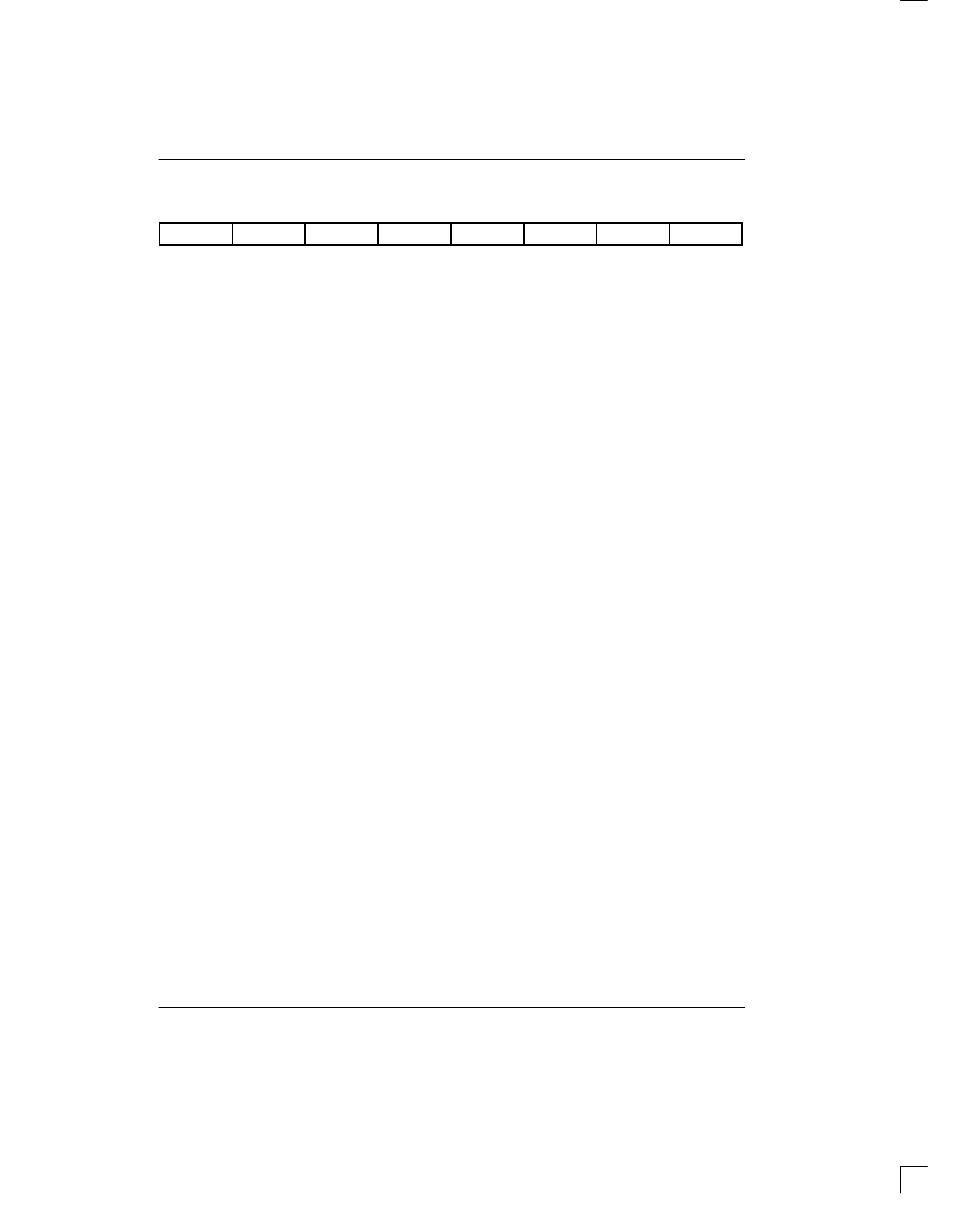

CCR3: COMMON CONTROL REGISTER 3 (Address=30 Hex)

(MSB)

(LSB)

ESMDM

ESR

P16F

RSMS

PDE

TLD

TLU

LIRST

SYMBOL

POSITION

NAME AND DESCRIPTION

ESMDM

CCR3.7

Elastic Store Minimum Delay Mode. See Section 10.3 for details.

0=elastic stores operate at full two frame depth

1=elastic stores operate at 32–bit depth

ESR

CCR3.6

Elastic Store Reset. Setting this bit from a zero to a one will force the elas-

tic stores to a known depth. Should be toggled after SYSCLK has been

applied and is stable. Must be cleared and set again for a subsequent

reset.

P16F

CCR3.5

Function of Pin 16.

0=Receive Loss of Sync (RLOS).

1=Loss of Transmit Clock (LOTC).

RSMS

CCR3.4

RSYNC Multiframe Skip Control. Useful in framing format conversions

from D4 to ESF.

0=RSYNC will output a pulse at every multiframe

1=RSYNC will output a pulse at every other multiframe note: for this bit to

have any affect, the RSYNC must be set to output multiframe pulses

(RCR2.4=1 and RCR2.3=0).

PDE

CCR3.3

Pulse Density Enforcer Enable.

0=disable transmit pulse density enforcer

1=enable transmit pulse density enforcer

TLD

CCR3.2

Transmit Loop Down Code (001).

0=transmit data normally

1=replace normal transmitted data with loop down code

TLU

CCR3.1

Transmit Loop Up Code (00001).

0=transmit data normally

1=replace normal transmitted data with loop up code

LIRST

CCR3.0

Line Interface Reset. Setting this bit from a zero to a one will initiate an

internal reset that affects the slicer, AGC, clock recovery state machine and

jitter attenuator. Normally this bit is only toggled on power–up. Must be

cleared and set again for a subsequent reset.

LOOP CODE GENERATION

When either the CCR3.1 or CCR3.2 bits are set to one,

the DS2151Q will replace the normal transmitted pay-

load with either the Loop Up or Loop Down code respec-

tively. The DS2151Q will overwrite the repeating loop

code pattern with the framing bits. The SCT will con-

tinue to transmit the loop codes as long as either bit is

set. It is an illegal state to have both CCR3.1 and

CCR3.2 set to one at the same time.

PULSE DENSITY ENFORCER

The SCT always examines both the transmit and

receive data streams for violations of the following rules

which are required by ANSI T1.403–199X:

– no more than 15 consecutive zeros

– at least N ones in each and every time window

of 8 x (N +1) bits where N=1 through 23.

Violations for the transmit and receive data streams are

reported in the RIR2.2 and RIR2.1 bits respectively.