1 mv64360 interrupt controller, Mv64360 interrupt controller, Table 4-7 – Motorola CPCI-6115 User Manual

Page 87: Mv64360 interrupt assignments

Interrupt Handling

Functional Description

CPCI-6115 CompactPCI Single Board Computer Installation and Use (6806800A68D)

85

4.4.2.1

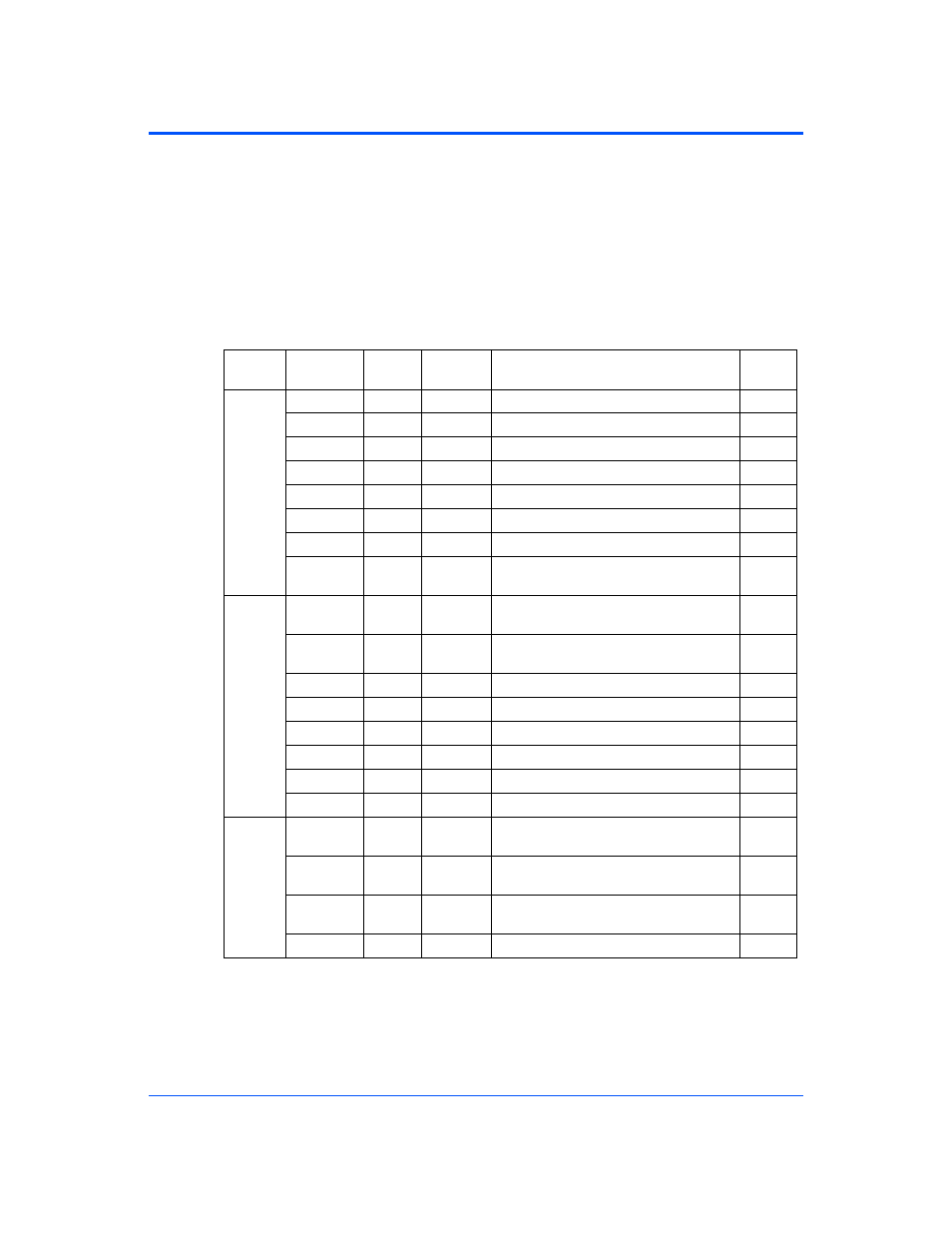

MV64360 Interrupt Controller

The CPCI-6115 uses the MV64360 interrupt controller to route internal and external interrupt

requests to the CPU and the PCI bus. The MV64360 interrupt controller registers are

implemented as part of the CPU interface unit in order to have minimum read latency from CPU

interrupt handler. The external interrupt sources use the GPP interface to register external

interrupts. The following table shows the CPCI-6115 interrupt assignment to MV64360 GPP

pins:

These notes apply to

1.

The interrupting device is addressed from the MV64360 PCI Bus 0.0.

2.

The interrupting device is addressed from the MV64360 PCI Bus 1.0

Table 4-7 MV64360 Interrupt Assignments

GPP

Group

MV64360

Edge/L

evel

Polarity

Interrupt Source

Notes

0

GPP[0]

Level

High

COM1 || COM2

3

GPP[1]

Level

Low

Unused

GPP[2]

Level

Low

ABORT#

GPP[3]

Level

Low

RTC || Thermostat output

6

GPP[4]

Level

Low

Unused

GPP[5]

Level

Low

Unused

GPP[6]

Level

Low

MV64360 WDNMI# interrupt

GPP[7]

Level

Low

BCM5421S PHY 1 INTR# || BCM5421S

PHY 2 INTR# || BCM5421S PHY 3 INTR#

2

GPP[16]

Level

Low

PCI Bus 1.0 - PMC1 INTA#, PMC1 INTC#,

21555

2

GPP[17]

Level

Low

PCI Bus 1.0 - PMC1 INTB#, PMC1 INTD#,

IDE

2

GPP[18]

Level

Low

PCI Bus 0.0 - PMC2 INTA#, PMC2 INTC#

1

GPP[19]

Level

Low

PCI Bus 0.0 - PMC2 INTB#, PMC2 INTD#

1

GPP[20]

Level

Low

CompactPCI Bus - INTA#

5

GPP[21]

Level

Low

CompactPCI Bus - INTB#

5

GPP[22]

Level

Low

CompactPCI Bus - INTC#

5

GPP[23]

Level

Low

CompactPCI Bus - INTD#

5

3

GPP[24]

Reserved for SROM initialization active

InitAct output

GPP[25]

Reserved for Watchdog Timer WDE#

output

GPP[26]

Reserved for Watchdog Timer WDNMI#

output

GPP[27]

Reserved for future device interrupt