4 abort/reset switch, 5 on-board connectors and headers, 1 j19, front panel asynchronous serial port – Motorola CPCI-6115 User Manual

Page 54: Abort/reset switch, On-board connectors and headers, J19, front panel asynchronous serial port, Table 3-2, Com1 pin assignments, j19

CPCI-6115 CompactPCI Single Board Computer Installation and Use (6806800A68D)

Controls, LEDs, and Connectors

ABORT/Reset Switch

52

3.4

ABORT/Reset Switch

The CPCI-6115 contains a single push button switch that provides both ABORT and RESET

functions. When the switch is depressed for less than 3 seconds, an ABORT interrupt is

generated to the processor. If the switch is held for more than 3 seconds, a board hard reset is

generated.

3.5

On-Board Connectors and Headers

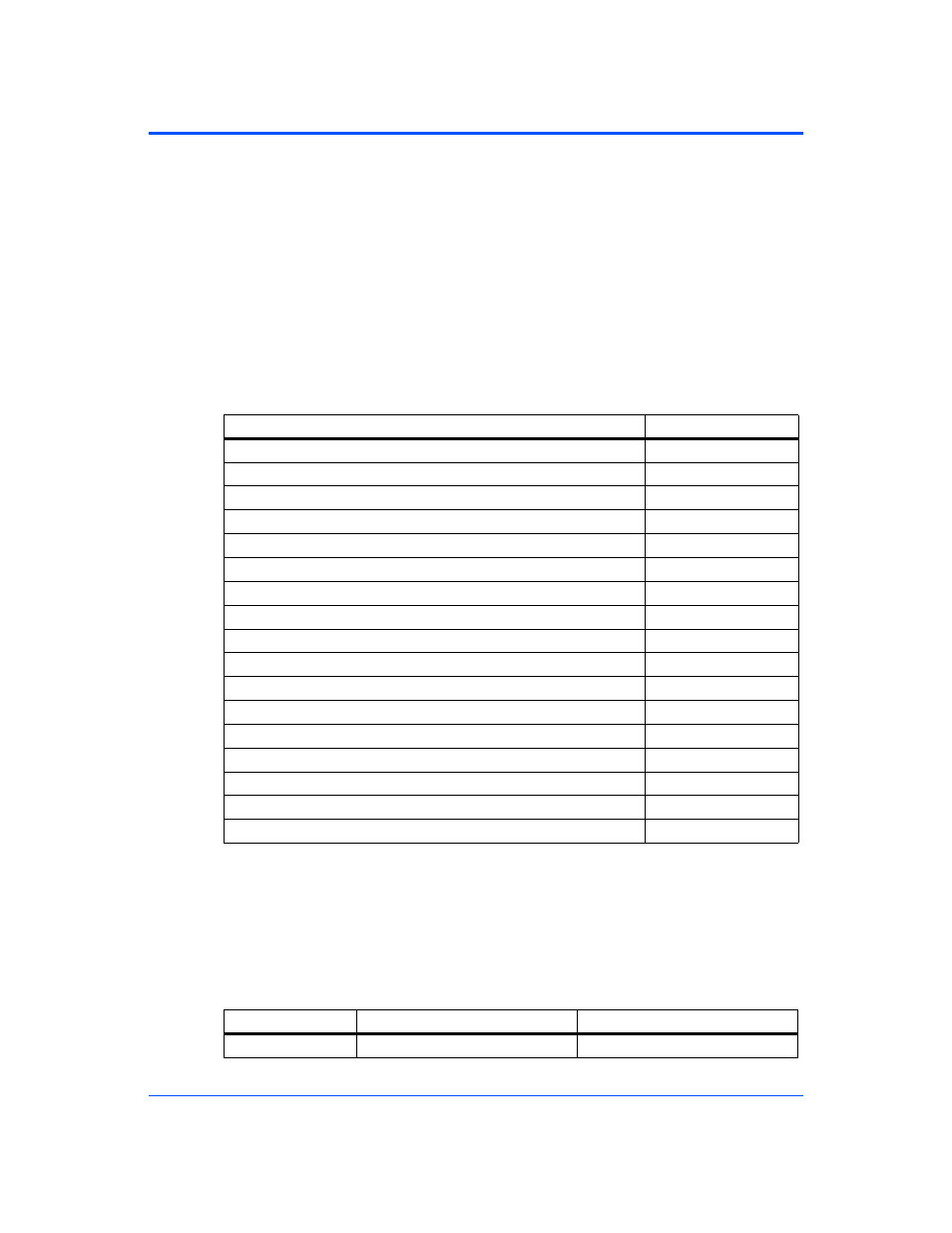

The CPCI-6115 CPU board provides the on-board connectors and jumper headers listed in the

next table. Use the links in the Location column to go to the description and pin assignment for

each connector.

3.5.1

J19, Front Panel Asynchronous Serial Port

An RJ-45 receptacle is located on the front panel of the CPCI-6115 CPU board to provide the

interface to the COM1 serial port. This port is configured as DTE. The pin assignments for this

connector are as follows:

Connector/Header

Location

CPCI-6115 CompactPCI Connectors ( J1/J2 )

CPCI-6115 CompactPCI User I/O Connector (J3)

CPCI-6115 CompactPCI Connector (J4)

N/A

CPCI-6115 CompactPCI User I/O Connector (J5)

CPCI-6115 PCI Mezzanine Card (PMC) Connectors (J11/J21)

CPCI-6115 PCI Mezzanine Card (PMC) Connectors (J12/J22)

CPCI-6115 PCI Mezzanine Card (PMC) Connectors (J13/J23)

CPCI-6115 PCI Mezzanine Card (PMC) Connectors (J14/J24)

Boundary Scan JTAG Header (J16)

CPCI-6115 Riscwatch Header (J17)

Standalone Operation Select Header (J9)

CPCI-6115 Flash Boot Bank Select Header (J10)

Safe Start Header (J20)

Bus Mode Select Header (J6)

SROM Init Enable Header (J25)

Flash Bank A Write Protect Header (J99)

+/-12 V Present Header (J15)

Table 3-2 COM1 Pin Assignments, J19

Pin #

Signal

Direction

1

DCD

INPUT