3 default pci memory map, Default pci memory map, Table 8-2 – Motorola CPCI-6115 User Manual

Page 129: Suggested ppc memory map, Table 8-3, Default pci address map

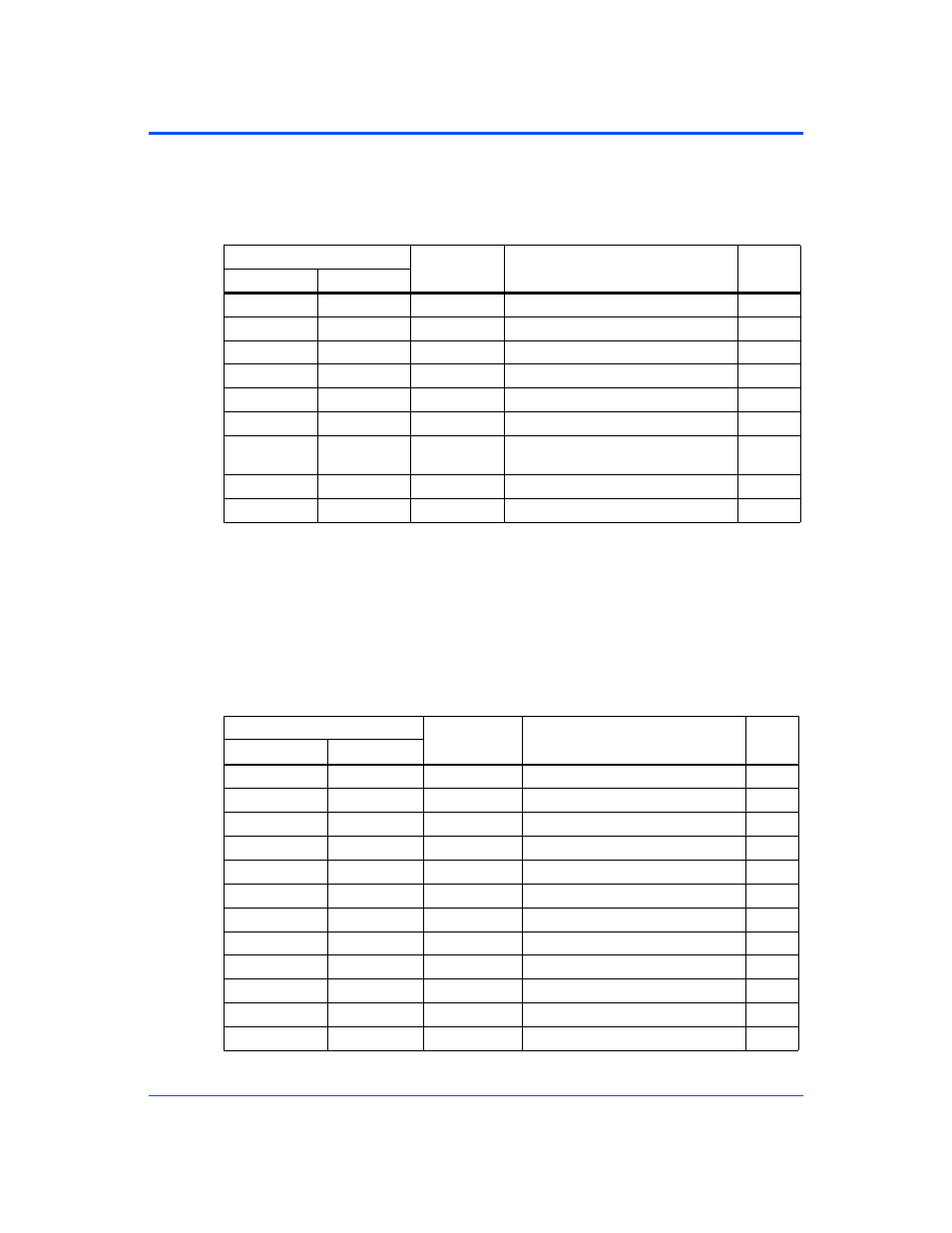

Default PCI Memory Map

Memory Maps

CPCI-6115 CompactPCI Single Board Computer Installation and Use (6806800A68D)

127

This is a suggested map only. Motorola developed firmware and software adheres to the

following mapping, but end user applications are free to select an alternate mapping.

1. The internal registers only occupy the first 64 KB but minimum address decoding resolution

is 1 MB.

8.2.3

Default PCI Memory Map

The MV64360 presents the following default PCI memory map after RESET negation.

Table 8-2 Suggested PPC Memory Map

Processor Address

Size

Definition

Notes

Start

End

0000 0000

top_dram-1

dram_size

System Memory (onboard DRAM)

8000 0000

9FFF FFFF

512 MB

PCI Bus 0 Memory Space

B000 0000

CFFF FFFF

512 MB

PCI Bus 1 Memory Space

F000 0000

F07F FFFF

8 MB

PCI Bus 0 I/O Space

F080 0000

F0FF FFFF

8 MB

PCI Bus 1 I/O Space

F100 0000

F10F FFFF

1 MB

MV64360 Internal Registers

1

F110 0000

F11F FFFF

1 MB

Device CS1* I/O System

Regs/NVRAM/RTC/UART

F200 0000

F5FF FFFF

64 MB

Flash Bank A

FF800 0000

FFFF FFFF

8 MB

Flash Bank B

Table 8-3 Default PCI Address Map

PCI Address

Size

Definition

No

tes

Start

End

0000 0000

007F FFFF

8 MB

DRAM Bank 0

0080 0000

00FF FFFF

8 MB

DRAM Bank 1

0100 0000

017F FFFF

8 MB

DRAM Bank 2

0180 0000

01FF FFFF

8 MB

DRAM Bank 3

0200 0000

0FFF FFFF

224 MB

Unassigned

1000 0000

11FF FFFF

32 MB

PCI Bus 1 P2P I/O Space

1200 0000

13FF FFFF

32 MB

PCI Bus 1 P2P Memory Space 0

1400 0000

1400 FFFF

64 KB

Internal Registers

1401 0000

1BFF FFFF

128 MB- 64 KB

Unassigned

1C00 0000

1C7F FFFF

8 MB

Device CS0*

1C80 0000

1CFF FFFF

8 MB

Device CS1*

1D00 0000

1DFF FFFF

16 MB

Device CS2*