5 system memory, System memory, Table 4-4 – Motorola CPCI-6115 User Manual

Page 81: System memory options

System Memory

Functional Description

CPCI-6115 CompactPCI Single Board Computer Installation and Use (6806800A68D)

79

4.3.5

System Memory

The CPCI-6115 consists of up to three banks of Double-Data-Rate SDRAMs. DDR SDRAM

supports two data transfers per clock cycle. The base memory device is a standard monolithic

DDR SDRAM, 8-bits wide, in a 66-pin TSOPII package. The CPCI-6115 can be populated with

up to three banks of memory onboard (nine devices per bank). One or two banks can be

populated with standard single DDR devices. If three banks are populated, chip-stacking

technology is used on the top side to accommodate two banks in a single-bank footprint. When

using the stacked parts, the two stacked banks (0 and 2) are identical, so a single SPD

EEPROM is used for them.

All memory configurations operate at DDR226 (133 MHz CLK).

WE[3:0],

DP[3:0]

X

X

DRAM PLL N

Divider [7:4],

[3:0]

X

Not used in sync mode

BADR[0]

Resistor

1

DRAM PLL NP

X

Not used in sync mode

BADR[1]

Resistor

1

DRAM PLL

HIKVCO

X

Not used in sync mode

BADR[2]

Resistor

1

DRAM PLL NP

0

PLL power down

1

PLL power up

(normal operation)

TxD0[6:1]

X

X

DRAM PLL M

Divider

X

Not used in sync mode

TxD0[7]

Resistor

0

JTAG Pad Calib

Bypass

0

Normal Operation

1

Bypass pad calibration

TxD1[1]

Resistor

0

Core PLL Bypass

0

Normal Operation

1

Bypass the core’s PLL

TxD1[4:2]

Resistors

000

Core PLL

Control

000

Tuning of the core PLL clock

tree.

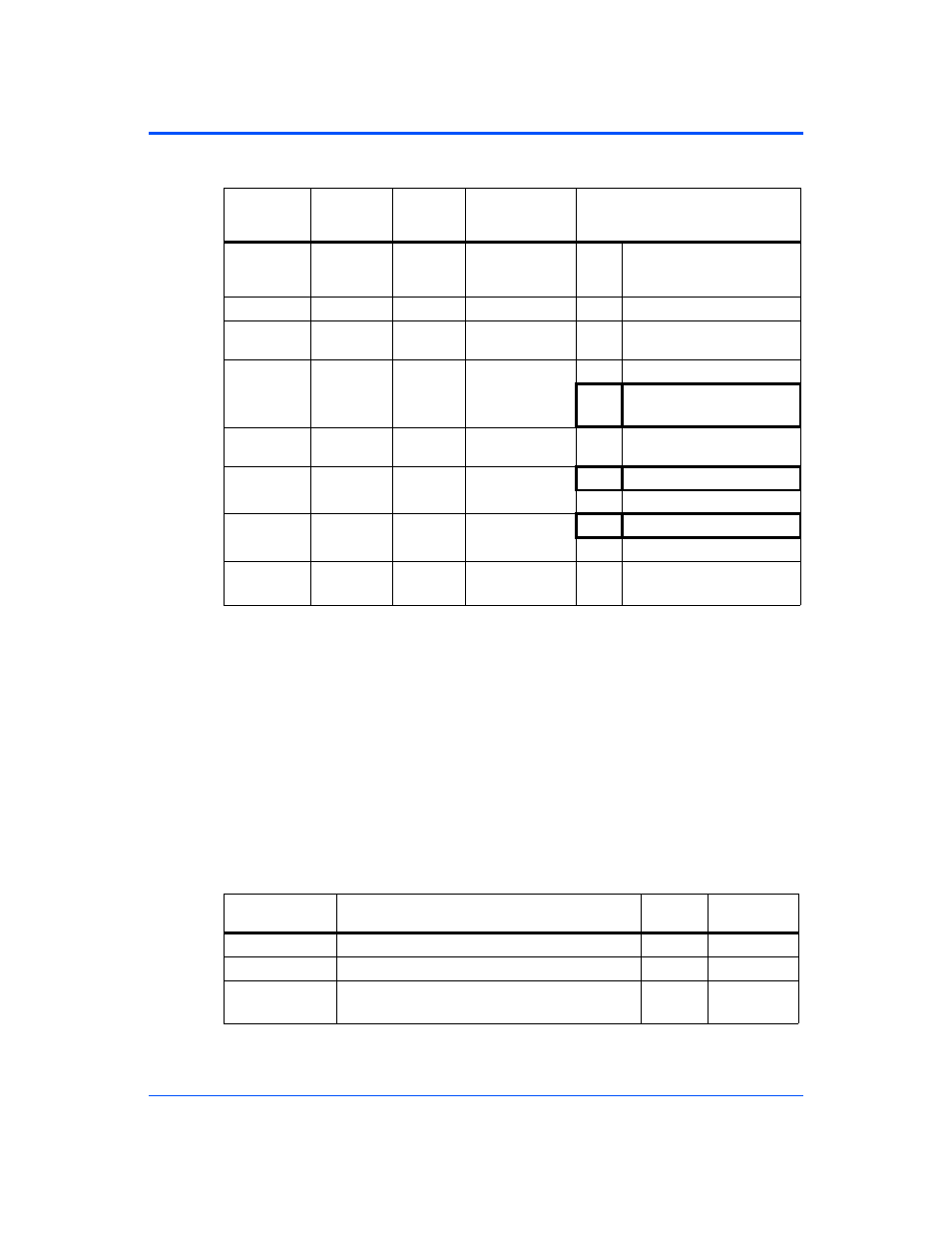

Table 4-3 MV64360 Power-Up Configuration Settings (continued)

Device AD

Bus Signal

Select

Option

Default

Power-Up

Setting

Description

State of Bit vs. Function

Table 4-4 System Memory Options

Organization

Memory Device

Device

Size

Bank Size

32 MB x 8

K4H560838F-TCB3 (133 MHz, CL=2.5)

256 MB

256 MB

64 MB x 8

K4H510838B-TCB3 (133 MHz, CL=2.5)

512 MB

512 MB

128 MB x 8

K4H1G0738M-TCB0 (133 MHz, CL=2.5)

K4H1G0838M-TCB0 (133 MHz, CL=2.5)

1 GB

Two banks of

512 MB