4 miscellaneous, 1 clock generation, 2 interrupt handling – Motorola CPCI-6115 User Manual

Page 86: Miscellaneous, Clock generation, Interrupt handling

CPCI-6115 CompactPCI Single Board Computer Installation and Use (6806800A68D)

Functional Description

Miscellaneous

84

4.4

Miscellaneous

The following described functions and features are also part of the CPCI-6115.

4.4.1

Clock Generation

The CPCI-6115 synchronizes its CompactPCI bus interface to the received PCI clock from the

J1-D6 connector pin. Onboard logic determines the CompactPCI operating mode by looking at

the state of the CompactPCI M66EN and PCIXCAP signals at the end of reset. The onboard

clock generator is then configured to provide the necessary clocks for the CompactPCI

interface. All other clocks for onboard resources are generated locally.

4.4.2

Interrupt Handling

The following sections further describe CPCI-6115 interrupt-related topics.

MONARCH#

The CPCI-6115 leaves the MONARCH# pin floating, causing any installed

processor PMC to operate as a slave module. Processor PMC monarch mode is not

supported.

IDSELB

These IDSELB pins are resistively coupled to the appropriate PCI AD pins.

REQB#

These REQB# pins are routed to the appropriate PCI bus arbiters.

GNTB#

These GNTB# pins are routed to the appropriate PCI bus arbiters.

M66EN

The CPCI-6115 has a weak pull-up on this signal. If this signal is grounded, as it is

when a 33 MHz PMC module is installed, it will force the corresponding PCI bus to

33 MHz operation. If the signal remains high, this will allow 66 MHz operation.

RESETOUT_L

The CPCI-6115 does not make any connection to RESETOUT_L.

EREADY

The EREADY signals from each PMC are routed board Presence Detect Register

for software readability.

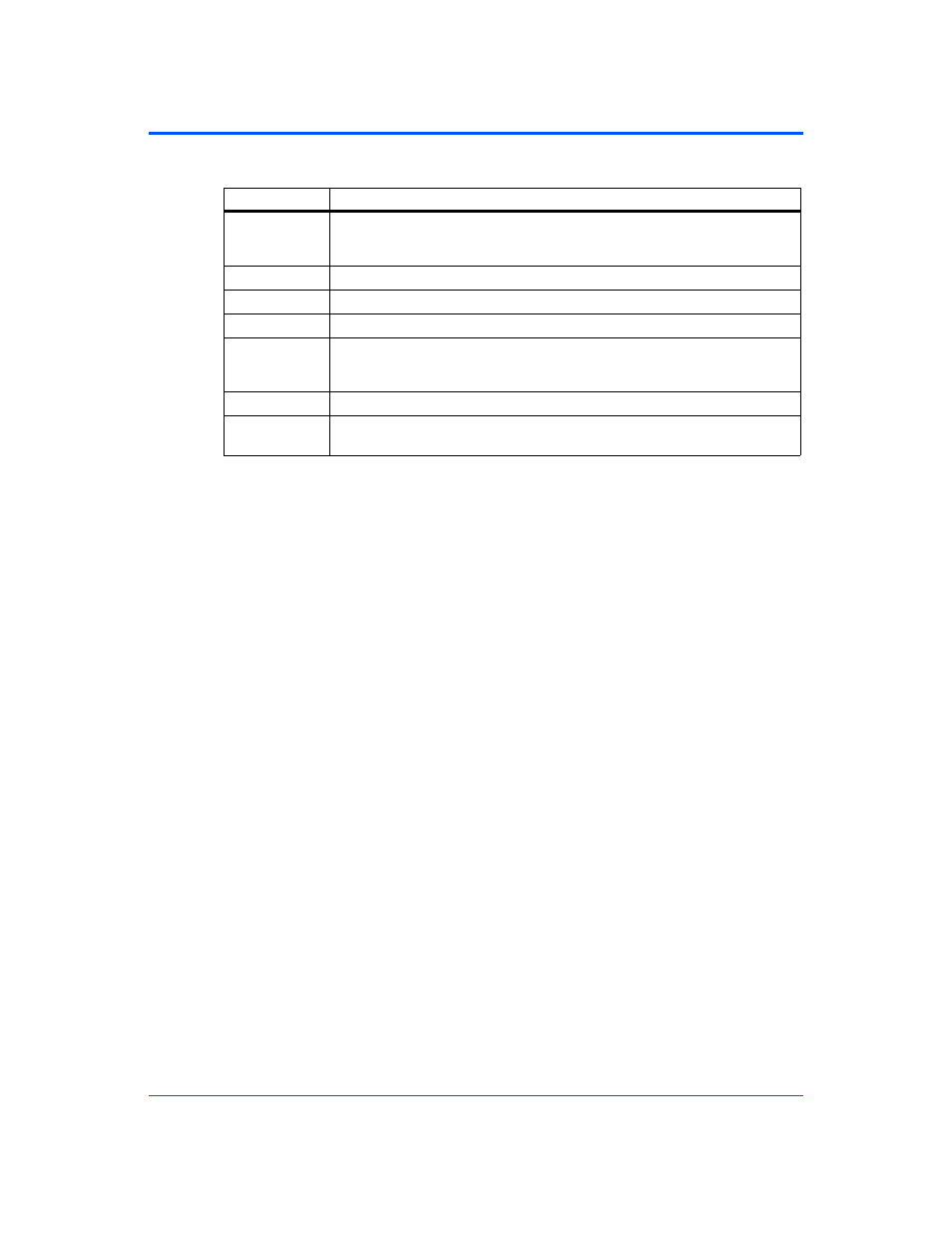

Table 4-6 Processor PMC Support (continued)

PrPMC Signal

Support