Memory maps, 1 overview, 2 memory maps – Motorola CPCI-6115 User Manual

Page 127: 1 default processor memory map, Overview, Default processor memory map, Table 8-1, Chapter 8, memory maps

8

CPCI-6115 CompactPCI Single Board Computer Installation and Use (6806800A68D)

125

Memory Maps

8.1

Overview

This chapter supplies information for use of the CPCI-6115 family of Single Board Computers

in a system configuration. Here you will find descriptions of the memory maps and software

initialization.

8.2

Memory Maps

There are three points of view for memory maps:

z

Mapping of all resources as viewed by the processor (MPU bus memory map)

z

Mapping of onboard resources as viewed by PCI local bus masters (PCI bus memory map)

z

Mapping of onboard resources as viewed by the CompactPCI bus

The following sections give a general description of the CPCI-6115 memory organization from

the above three points of view. Detailed memory maps can be found in the MCPN905

CompactPCI Single Board Computer Programmer’s Reference Guide (MCPN905A/PG).

8.2.1

Default Processor Memory Map

The MV64360 presents a default CPU memory map following RESET negation. The following

table shows the default Memory Map from the point of view of the Processor. Address bits

[35:32] are only relevant for the MPC7457 extended address mode and are not shown in the

following tables.

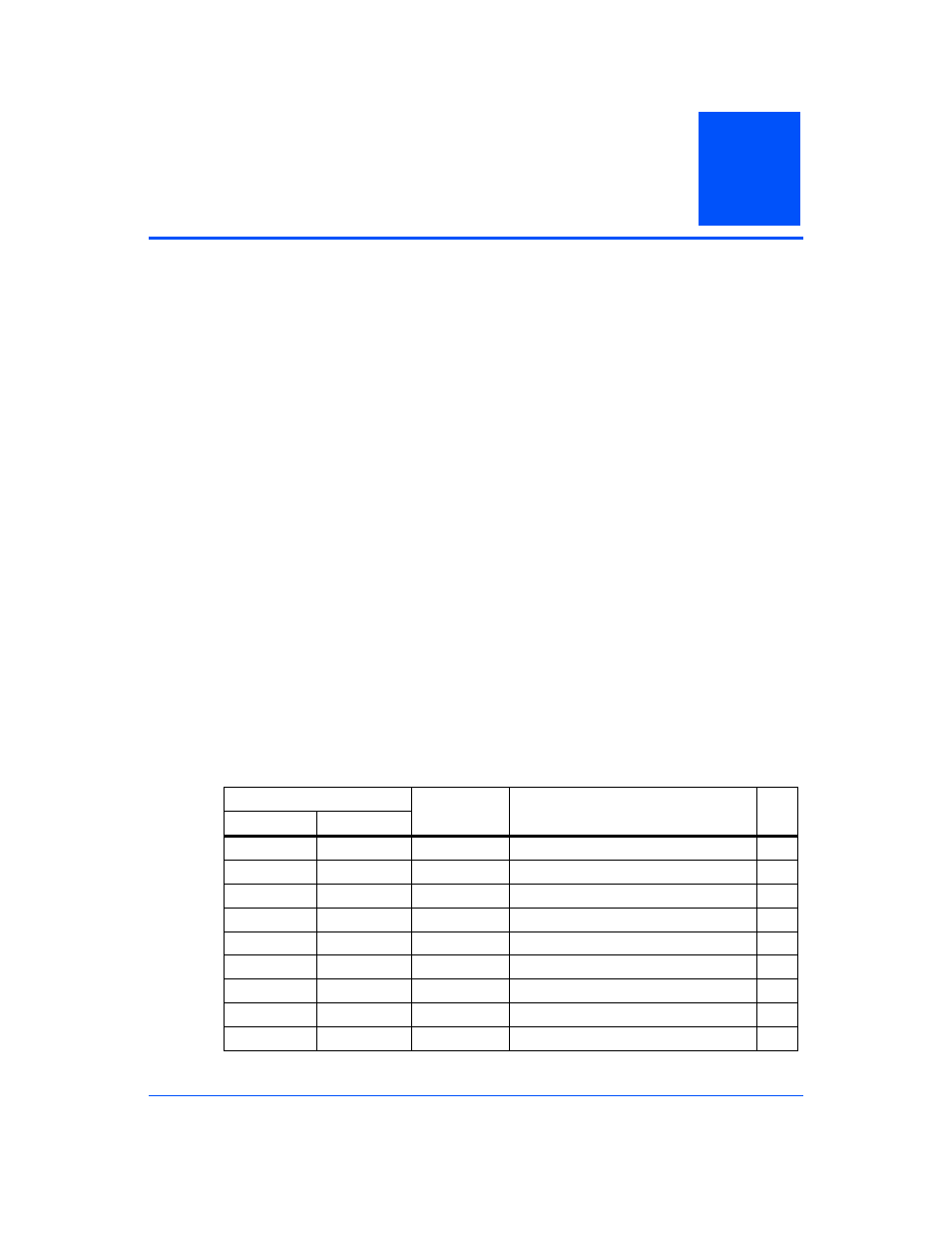

Table 8-1 Default Processor Memory Map

Processor Address

Size

Definition

No

tes

Start

End

0000 0000

007F FFFF

8 MB

DRAM Bank 0

0080 0000

00FF FFFF

8 MB

DRAM Bank 1

0100 0000

017F FFFF

8 MB

DRAM Bank 2

0180 0000

01FF FFFF

8 MB

DRAM Bank 3

0200 0000

0FFF FFFF

224 MB

Unassigned

1000 0000

11FF FFFF

32 MB

PCI Bus 0 I/O Space

1200 0000

13FF FFFF

32 MB

PCI Bus 0 Memory Space 0

1400 0000

1BFF FFFF

128 MB

Unassigned

1C00 0000

1C7F FFFF

8 MB

Device CS0*