12 stand-alone operation select header, 13 flash boot bank select header, Table 3-14 – Motorola CPCI-6115 User Manual

Page 66: Table 3-15, Flash boot bank select header pin assignments, j10

CPCI-6115 CompactPCI Single Board Computer Installation and Use (6806800A68D)

Controls, LEDs, and Connectors

Stand-Alone Operation Select Header

64

3.5.12

Stand-Alone Operation Select Header

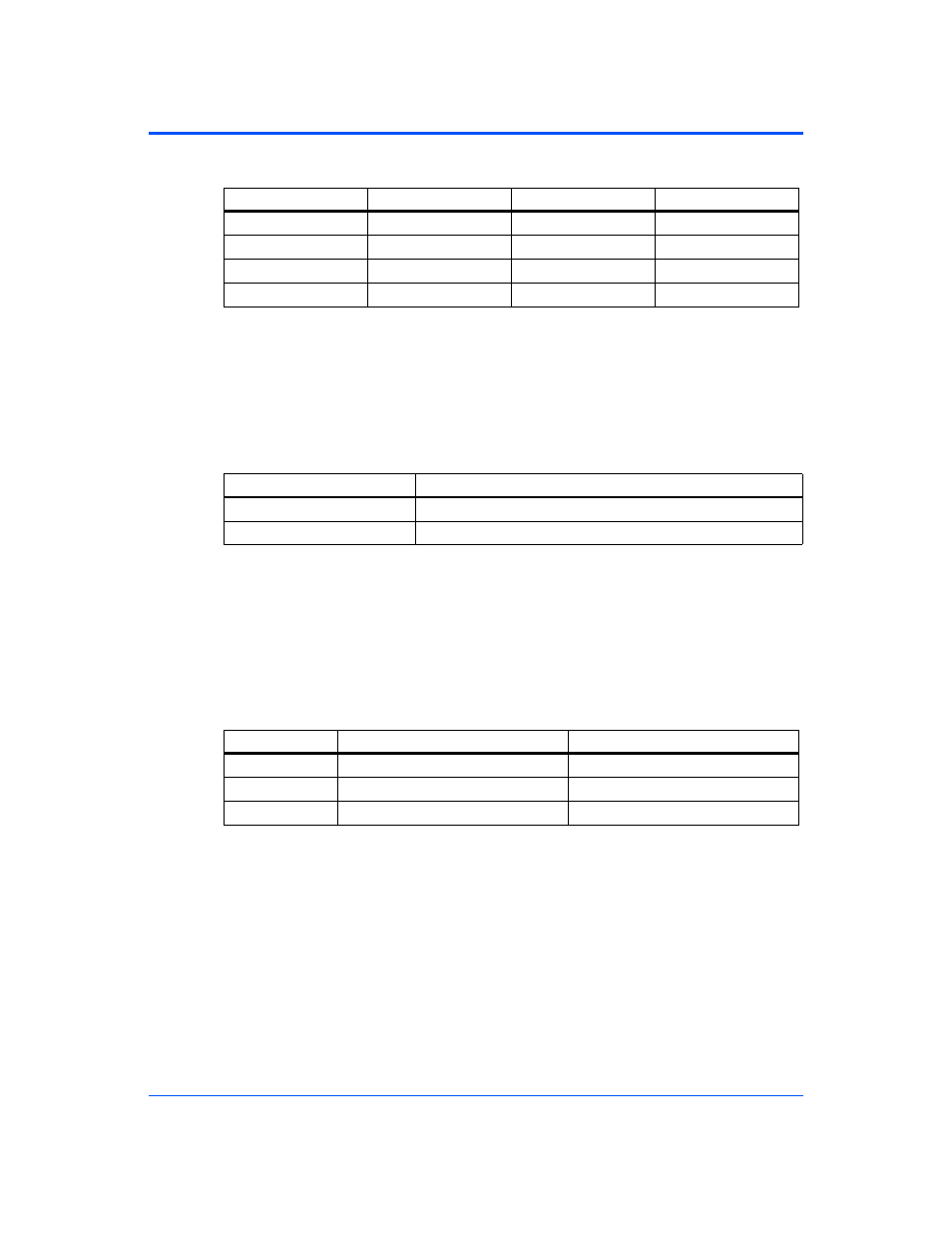

There is a 0.1", 2-pin header located on the CPCI-6115 to control standalone operation.

Standalone operation is selected when the jumper is installed and normal operation occurs

when the jumper is not installed. The pin assignments for this header are as follows:

3.5.13

Flash Boot Bank Select Header

There is a 0.1", 3-pin header on the CPCI-6115 to select the boot flash bank. No jumper or a

jumper installed between pins 1 and 2 will route the BOOTCS* signal to Flash Bank A and

device CS0* to Flash Bank B. A jumper installed between pins 2 and 3 routes BOOTCS* to

Flash Bank B and CS0* to Flash Bank A. The pin assignments for this header are as follows:

9

CPUTMS

10

NC

11

SRESET_L

12

NC

13

CPURST_L

14

KEY (no pin)

15

CHKSTPO_L

16

GND

Table 3-13 Processor JTAG/COP Header Pin Assignments, J17 (continued)

Pin

Signal

Pin

Signal

Table 3-14 Stand-Alone Operation Select Header Pin Assignments, J9

Pin

Signal

1

STAND_ALONE_L

2

GND

Table 3-15 Flash Boot Bank Select Header Pin Assignments, J10

Pin

Signal

Function

1

GND

1-2 Boot from Bank A

2

BANK_SEL

3

+3.3 V

2-3 Boot from Bank B