16 mv64360 reset configuration – Motorola CPCI-6115 User Manual

Page 78

CPCI-6115 CompactPCI Single Board Computer Installation and Use (6806800A68D)

Functional Description

MV64360 System Controller

76

4.3.4.16 MV64360 Reset Configuration

The MV64360 supports two methods of device initialization following reset:

z

Pins sampled on the deassertion of reset

z

Partial pin sample on deassertion of reset plus serial ROM initialization via the I

2

C bus for

user defined initialization.

The CPCI-6115 board supports both options. An onboard jumper setting is used to select the

option. If the pin sample only method is selected, then states of the various pins on the device

AD bus are sampled when reset is deasserted to determine the desired operating modes. The

following table describes the configuration options. Combinations of pullups, pulldowns and

jumpers are used to set the options. Some options are fixed and some are selectable at build

time by installing the proper pullup/pulldown resistor. Finally, some options may be selected

using an onboard jumper. Each option is described in the following table.

Using the SROM initialization method, any of the MV64360 internal registers or other system

components (that is, devices on the PCI bus) can be initialized. Initialization takes place by

sequentially reading 8 byte address/data pairs from the SROM and writing the 32-bit data to the

decoded 32-bit address until the data pattern matching the last serial data item register is read

from the SROM (default value 0xffffffff). An 8 KB EEPROM is provided onboard for this user

defined initialization of the MV64360.

22

I

CompactPCI Bus Interrupts - INTC#

23

I

CompactPCI Bus Interrupts - INTD#

MPP[17:16] PCI_1 Interrupts

MPP[19:18] PCI_0 Interrupts,

MPP[23:20] CompactPCI Interrupts

24

O

MV64360 SROM initialization active (InitAct)

25

O

Watchdog Timer Expired output (WDE#)

26

O

Watchdog Timer NMI output (WDNMI#)

27

I

Unused

28

O

PCI Bus 0.0 - PMC 2 secondary grant (GNTB#)

29

I

PCI Bus 0.0 - PMC 2 secondary request (REQB#)

30

O

PCI Bus 0.0 - PMC 2 grant

31

I

PCI Bus 0.0 - PMC 2 request

MPP[27:24] Miscellaneous

MPP[31:28] PCI_0 Arbitration Request-Grant Pairs

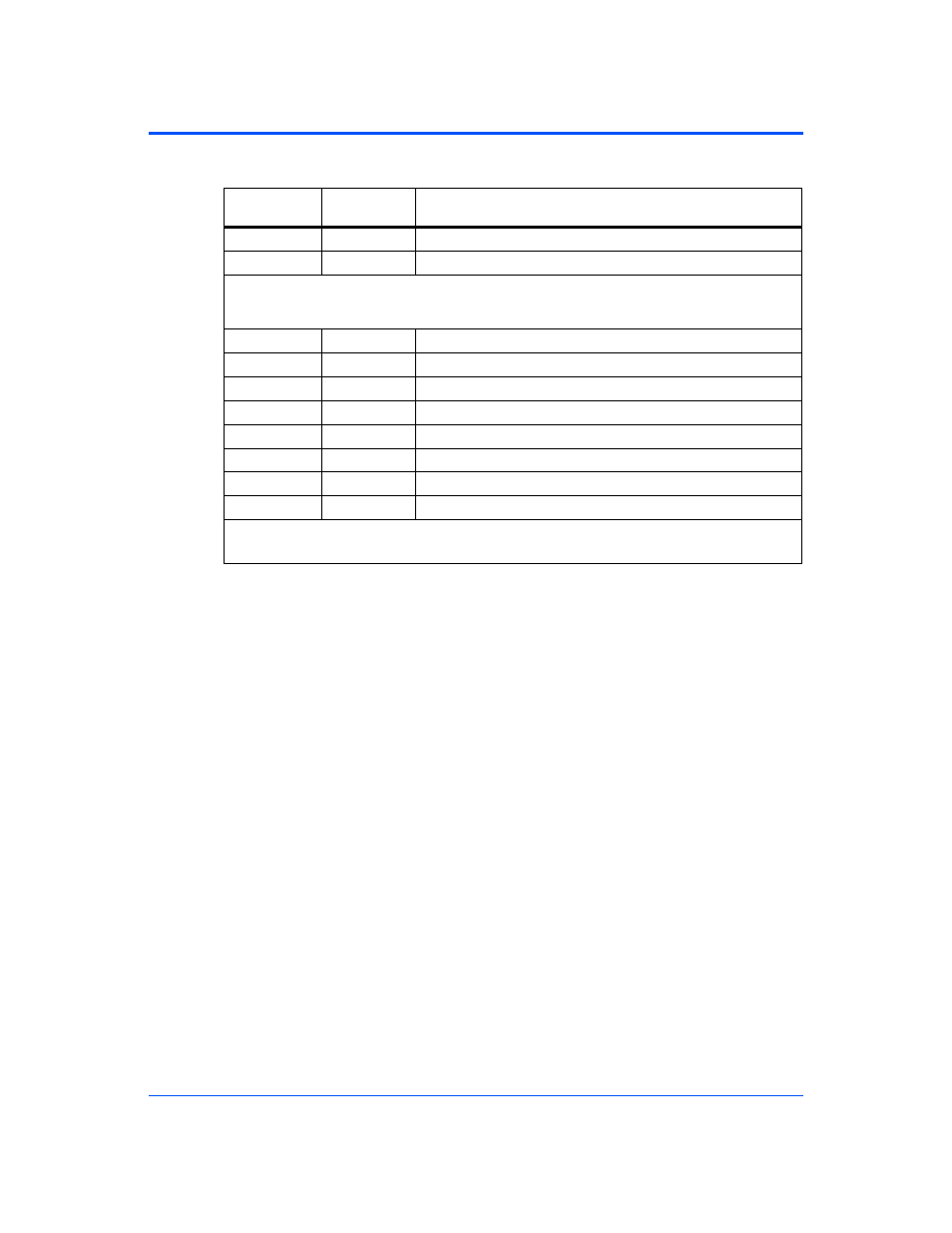

Table 4-2 MV64360 MPP Pin Function Assignments (continued)

MPP Pin

Number

Input/Output

Function