3 mv64360 32-bit interface to devices, 4 mv64360 dual pci/pci-x interfaces, 5 mv64360 integrated gigabit ethernet macs – Motorola CPCI-6115 User Manual

Page 74: Mv64360 32-bit interface to devices, Mv64360 dual pci/pci-x interfaces, Mv64360 integrated gigabit ethernet macs, Table 4-1, Device bus parameters

CPCI-6115 CompactPCI Single Board Computer Installation and Use (6806800A68D)

Functional Description

MV64360 System Controller

72

4.3.4.3

MV64360 32-bit Interface to Devices

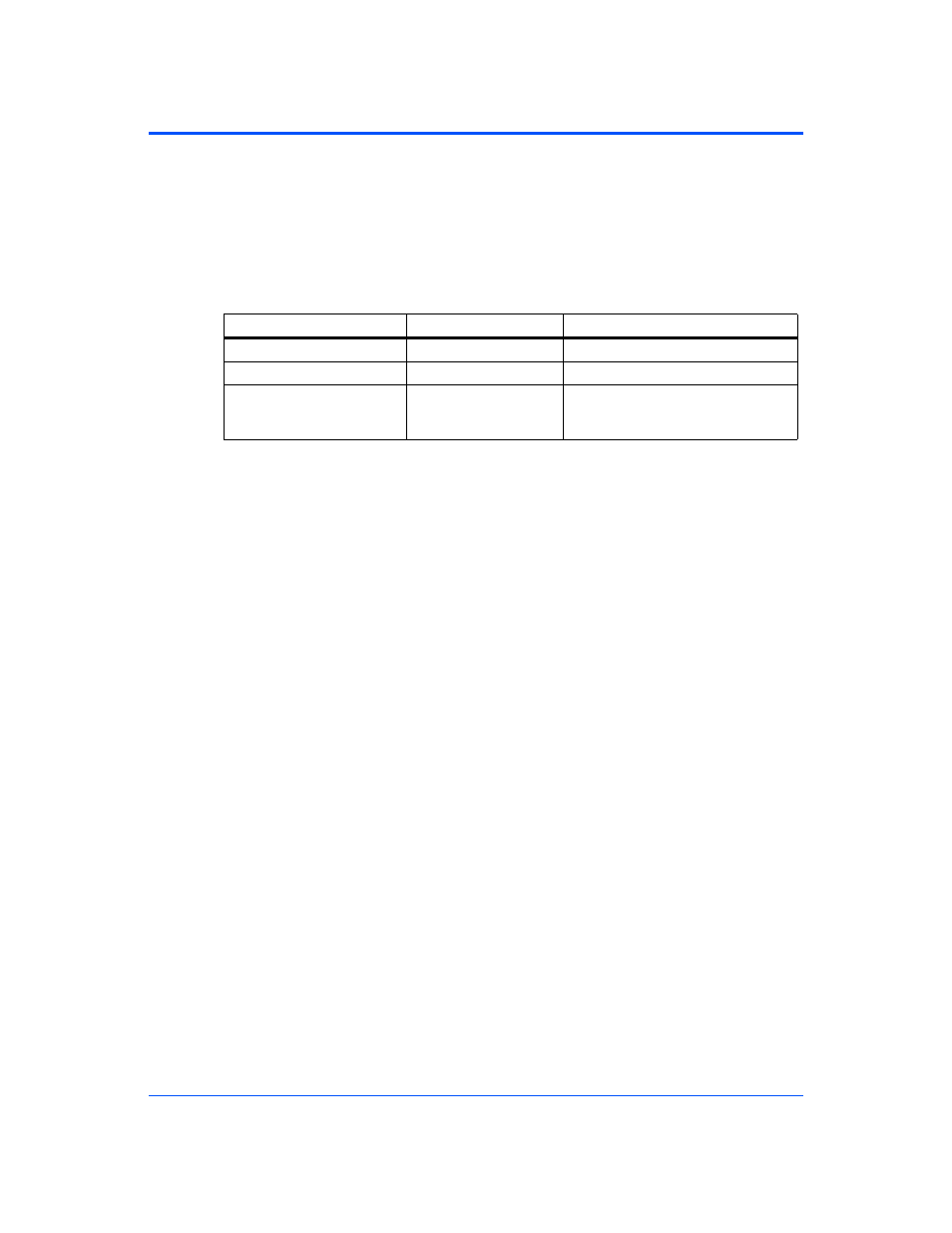

The device controller supports up to five banks of devices, of which three are used for Flash

Bank A and B, NVRAM/RTC, and serial ports on the CPCI-6115. Each bank supports up to 512

MB of address space, resulting in total device space of 1.5 GB. Each bank has its own

parameters register as shown in the following table.

4.3.4.4

MV64360 Dual PCI/PCI-X Interfaces

The MV64360 supports two PCI/PCI-X busses capable of operating up to 133 MHz in PCI-X

mode, and up to 66 MHz in conventional PCI mode, subject to routing and loading

considerations.

On the CPCI-6115, PCI Bus 0.0 is connected to PMC 2 and supports 32/64-bit transfers at

66/133 MHz PCI-X or 33/66 MHz PCI.

On the CPCI-6115, PCI Bus 1.0 is connected to PMC 1, the 21555 PCI-to-PCI bridge and the

IDE controller. The upper 32 bits of PCI Bus 1.0 on the MV64360 are multiplexed with the third

Gigabit Ethernet port (which may be routed to the front panel on the CPCI-6115), so PCI Bus

1.0 is only 32 bits wide when the third Gigabit Ethernet port is populated.

The IDE controller is a 33 MHz-only PCI device, so PCI Bus 1.0 is limited to 33 MHz PCI

transfers when the IDE controller is populated.

The MV64360 PCI interfaces are fully PCI Rev. 2.2 and PCI-X compliant. The MV64360

contains all the required PCI configuration registers. All internal registers, including the PCI

configuration registers, are accessible from the CPU bus or the PCI bus.

4.3.4.5

MV64360 Integrated Gigabit Ethernet MACs

The CPCI-6115 supports two 10/100/1000Base-T full duplex Ethernet ports connected to the

J3 connector for support of PICMG 2.16 I/O. The CPCI-6115 also routes the third Gigabit

Ethernet port to an RJ-45 connector on the front panel. The CPCI-6115 supports ports

configured to the 10/100 megabits/s MII interface and the 1 Gbps GMII interface. Receive and

transmit buffer management is based on buffer-descriptor linked list. Descriptors and data

transfers are performed by the port dedicated SDMA. Each board is assigned two Ethernet

Station Addresses.

The MV64360 does not integrate a Physical Layer for the Ethernet interfaces, so external PHYs

are required. On the CPCI-6115, the PHY device is a BroadCom BCM5421S

10/100/1000Base-T Gigabit Transceiver with SERDES Interface. This device was chosen for its

small footprint (8mm x 14mm) and low power (1 watt).

Table 4-1 Device Bus Parameters

Device

Device ID

Parameter Description

Flash Bank A

Device Bus Bank 0

Bank width 32-bit, parity disabled

Flash Bank B

Device Bus Boot Bank

Bank width 32-bit, parity disabled

Real Time Clock

Board Specific Register

Serial Ports

Device Bus Bank 1

Bank width 8-bit, parity disabled