8 address decoding with the 21555, 9 l1, l2 and l3 cache, 10 system memory – Motorola CPCI-6115 User Manual

Page 132: Address decoding with the 21555, L1, l2 and l3 cache, Table 8-6, Apollo l3cr register assignments

CPCI-6115 CompactPCI Single Board Computer Installation and Use (6806800A68D)

Memory Maps

Address Decoding with the 21555

130

8.2.8

Address Decoding with the 21555

The 21555 implements multiple base address registers on both the primary and secondary

interfaces that denote separate address ranges for both downstream and upstream

transactions. It also has base registers for access to its Control and Status Register (CSR)

space. Consequently, on the primary interface (CompactPCI bus) the 21555 responds only to

those transactions which are in the address range defined by one of the base address ranges.

All other addresses are ignored. The same is true for transactions on the secondary interface

(local PCI bus).

The address ranges defined by the primary base address registers reside in the primary or

system address map. The address ranges defined by the secondary base address registers

reside in the secondary or local address map. Each of these address maps is independent of

each other. The 21555 provides address translation between these two address maps when

forwarding transactions upstream or downstream.

Recommendations for CompactPCI mapping can be found in the MCPN905 CompactPCI

Single Board Computer Programmer’s Reference Guide (MCPN905A/PG).

8.2.9

L1, L2 and L3 Cache

The CPCI-6115 supports the MPC7457 processor on-chip L1 and L2 caches with 2 MB of

external L3 cache installed. The CPCI-6115 L3 memory consists of two 8 megabit (256Kx36,

300 MHz, 1.9 ns access) devices providing a total of 2 MB of memory. Data parity checking

should be enabled. The following settings assume a processor speed of 1000 MHz and L3 clock

speed of 200 MHz.

Refer to the PowerPC

™

Apollo Microprocessor Implementation Definition Book IV for more

information (Addendum to SC-Vger Book IV Version - 1.0 04/21/00).

8.2.10

System Memory

The CPCI-6115 system memory capability is controlled through an I

2

C compatible serial

controller integrated into the MV64360 system controller.

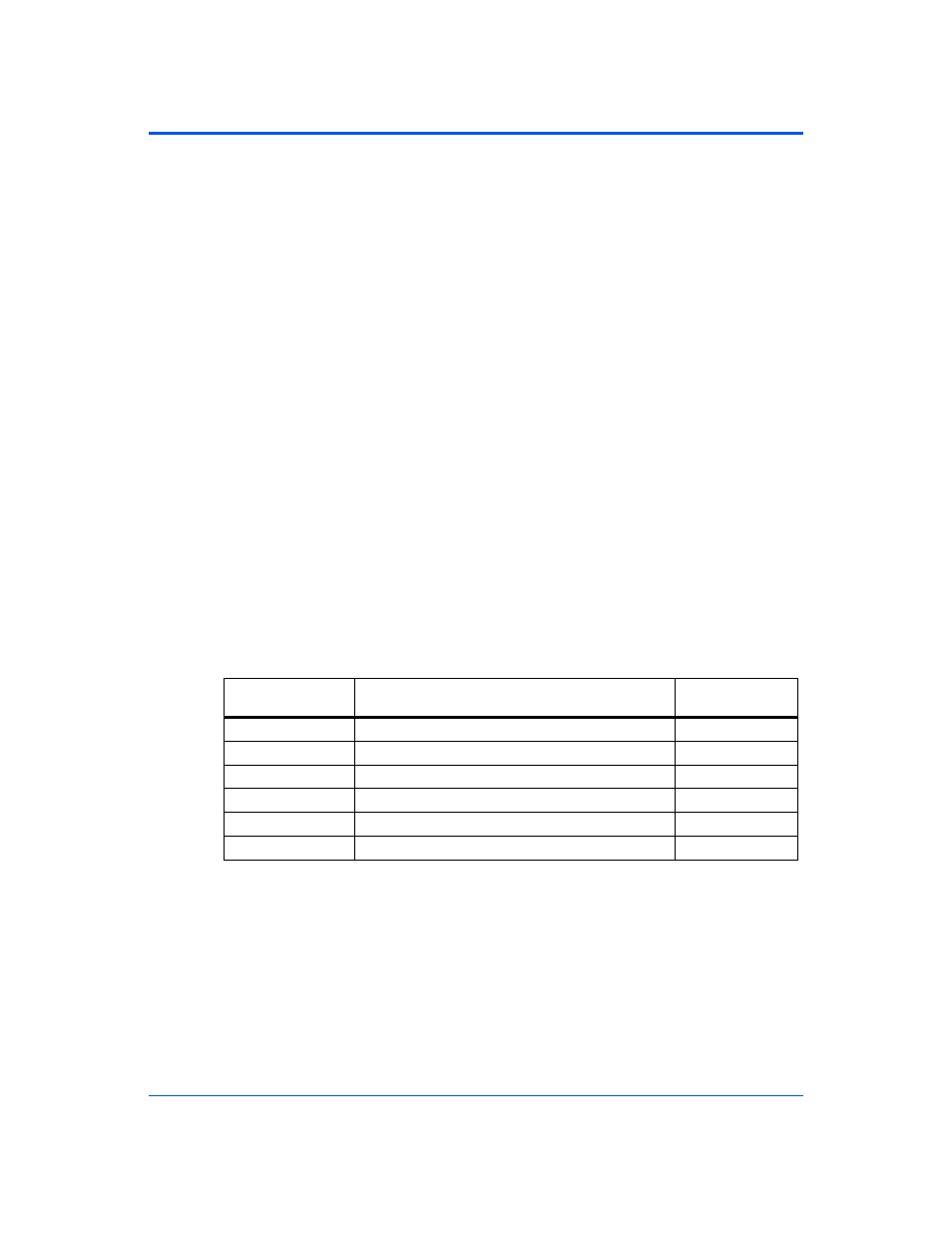

Table 8-6 Apollo L3CR Register Assignments

Apollo L3CR

Register

Description

Value

L3SIZ

L3 size, 1 MB

0b

L3RT

L3 SRAM type, DDR SRAM

00b

L3PE

L3 data parity checking enable, on

1b

L3CLK

L3 Clk speed; 266 MHz, divide by 5

111b

L3CKSP

L3 clock sample point, 4 clocks

10b

L3PSP

L3 P-clock sample point, 3 clocks

011b