6 flash memory, 7 nvram, real-time clock, watchdog timer, Flash memory – Motorola CPCI-6115 User Manual

Page 82: Nvram, real-time clock, watchdog timer, Table 4-5, Bank a flash options

CPCI-6115 CompactPCI Single Board Computer Installation and Use (6806800A68D)

Functional Description

Flash Memory

80

4.3.6

Flash Memory

The CPCI-6115 contains two banks of flash memory accessed via the device controller bus

contained within the MV64360 chip. Bank B consists of two Intel StrataFlash +3.3 V devices,

configured to operate in 16-bit mode, to form a 32-bit flash bank. Bank B provides a minimum

of 8 MB of flash memory.

Bank A consists of two Intel StrataFlash +3.3 V devices, configured to operate in 16-bit mode,

to form a 32-bit flash bank. The following table defines the flash type and size options for Bank

A. The CPCI-6115 standard product is built with the 128 megabit devices. These Intel

StrataFlash devices support page read mode operations with a 8-byte page size per device.

Since the StrataFlash initial access time is 150ns, onboard hardware is used to guarantee initial

access timing using the Device port READY# signal.

A flash write protect header is provided on the CPCI-6115 to enable write protection of the

entire Bank A flash via the device VPEN pins when the jumper is not installed. Bank A write

protection can also be enabled by software using the System Register 2 FLASH_WP bit in the

MV64360 when the jumper is installed.

There is a boot bank select jumper on the CPCI-6115 that selects either Flash Bank A or Bank

B as the boot bank. This jumper effectively routes the MV64360 BOOTCS# pin to either Bank

A/Bank B and chip select CS0# to the other bank (Bank B/Bank A).

4.3.7

NVRAM, Real-Time Clock, Watchdog Timer

An SGS-Thompson M48T37V device is connected to the MV64360 device controller bus. This

device provides 32 KB of nonvolatile static RAM, a real-time clock and a watchdog function.

Refer to the M48T37V Data Sheet for programming information. The M48T37V consists of two

parts:

z

One 44-pin 330mil SO device that contains the RTC, the oscillator, the power fail detection,

the watchdog timer logic, 32 KB of SRAM and gold-plated sockets for the SNAPHAT

battery.

z

One SNAPHAT that houses the battery and the crystal.

The SNAPHAT package is mounted on top of the SO MT48T37V device after the completion

of the surface mount process.

The watchdog timer can generate a timeout period of 62.5 msec to 128 seconds. The output of

the watchdog timer can be programmed to generate an interrupt or reset the board if enabled.

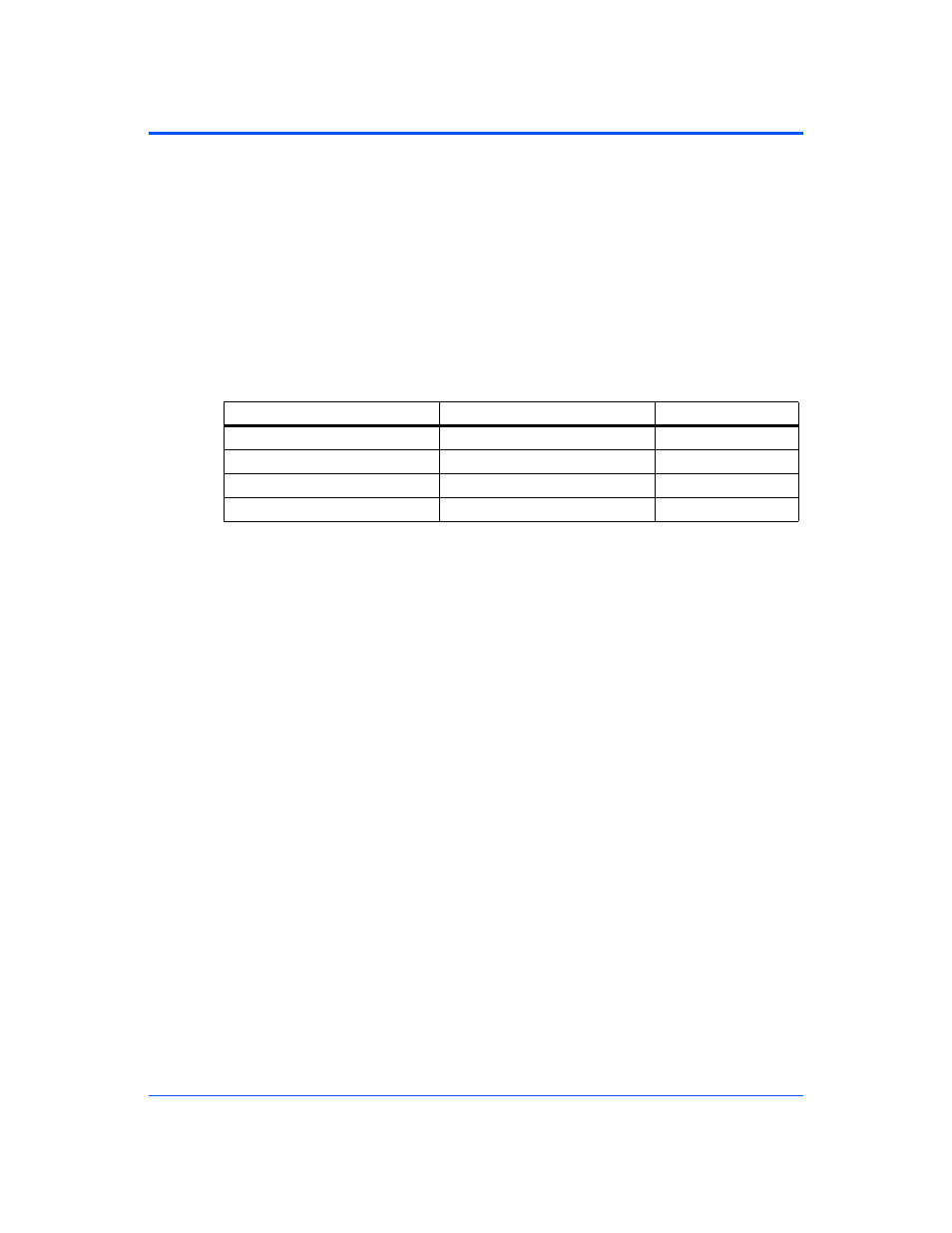

Table 4-5 Bank A Flash Options

Flash Bank Size

Intel Part Number

Device Size

8 MB

28F320J3D

32 megabit

16 MB

28F640J3D

64 megabit

32 MB

28F128J3D

128 megabit

64 MB

28F256P3

256 megabit