Introduction, 1 features, Features – Motorola CPCI-6115 User Manual

Page 27: Table 1-1, Cpci-6115 features, Chapter 1, introduction

1

CPCI-6115 CompactPCI Single Board Computer Installation and Use (6806800A68D)

25

Introduction

1.1

Features

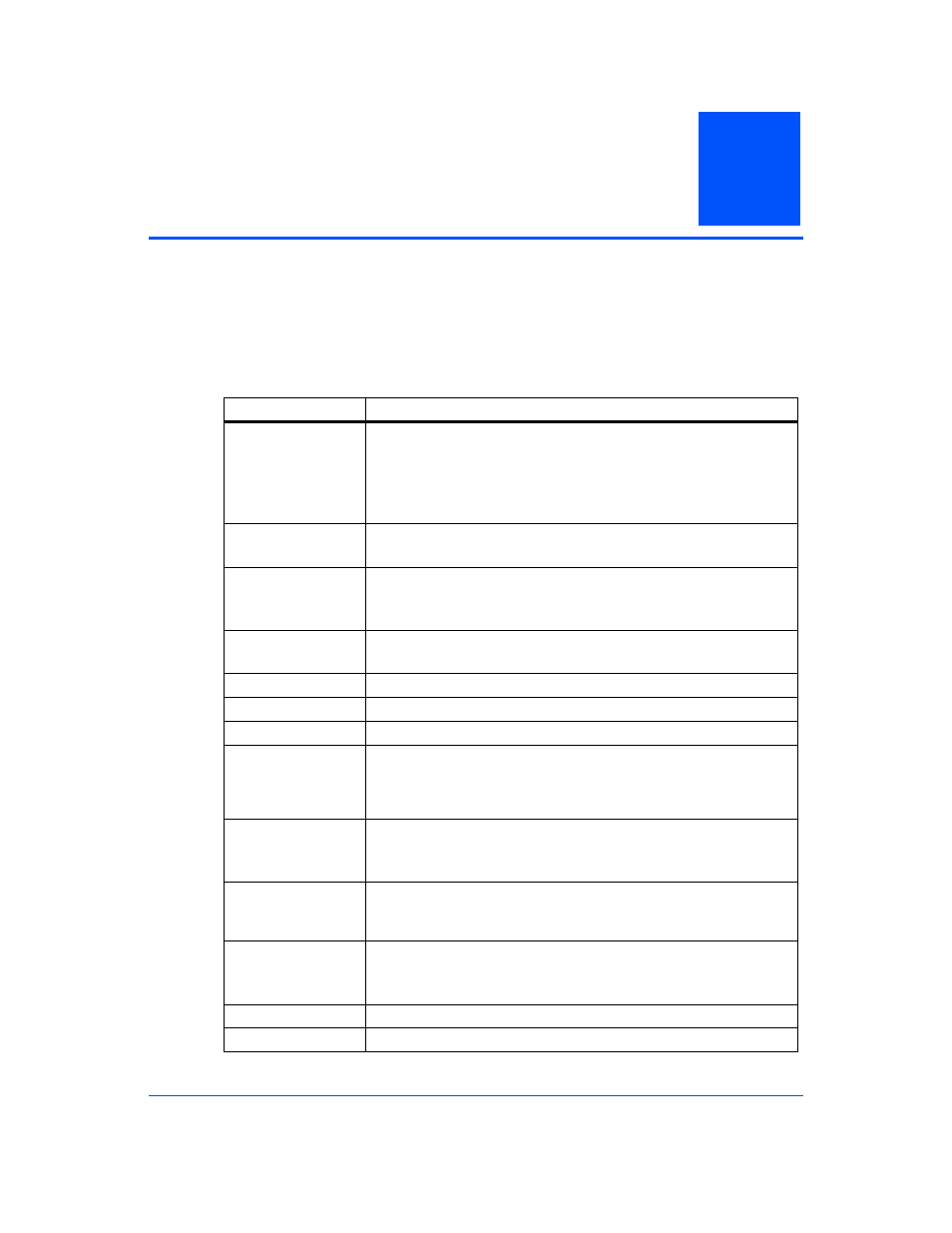

The following table summarizes the features of the CPCI-6115 Single Board Computer (SBC).

The CPCI-6115 was formerly offered as the MCPN905 SBC.

Table 1-1 CPCI-6115 Features

Feature

Description

Processor

Single MPC7457 Processor

Core Frequency to 1.0 GHz

Bus Clock Frequency of 133 MHz

Integrated L1 and L2 cache

Address and data bus parity

L3 Cache

1 MB or 2 MB DDR back side L3 Cache @ 266 MHz

Data bus parity

Flash

Bank A: 32 MB soldered flash using two Intel StrataFlash devices.

Bank B: 8 MB soldered flash using two Intel StrataFlash devices.

Bank A/B Reset vector jumper selectable

SDRAM

Double-Bit-Error detect, Single-Bit-Error correct across 72 bits.

Up to 1.5 GB of DDR266 (133 MHz) SDRAM onboard memory

Memory Controllers

Provided by Marvell MV64360 System Memory Controller.

PCI Host Bridges

Provided by Marvell MV64360 System Memory Controller.

Interrupt Controller

Provided by Marvell MV64360 System Memory Controller.

PCI Interfaces

One local PCI/PCI-X bus supporting 32/64-bit, 33/66 MHz PCI or 66/133

MHz PCI-X to PMC2.

One local PCI bus supporting 32-bit, 33 MHz PCI to PMC 1, the 21555 PCI

bridge, and IDE controller.

Ethernet Interface

Three Gigabit Ethernet channels provided by the Marvell MV64360

Two to J3 for PICMG 2.16 compliance

One to front panel

SEEPROM

Two 8 KB dual-address I2C SEEPROM devices for Vital Product Data and

user configuration data

Industry standard SPD for onboard and mezzanine board memory.

CompactPCI Interface

Intel 21555 PCI-to-PCI Bridge

64-bit, 33/66 MHz PCI to CompactPCI bus

Peripheral Slot operation

Form Factor

Single slot 6U CompactPCI

RTC/NVRAM

32KB NVRAM/RTC/WDT provided by M48T37V