10 boundary scan jtag header, 11 processor jtag/cop header, Table 3-12 – Motorola CPCI-6115 User Manual

Page 65: Boundary scan jtag header pin assignments, j16, Table 3-13, Processor jtag/cop header pin assignments, j17

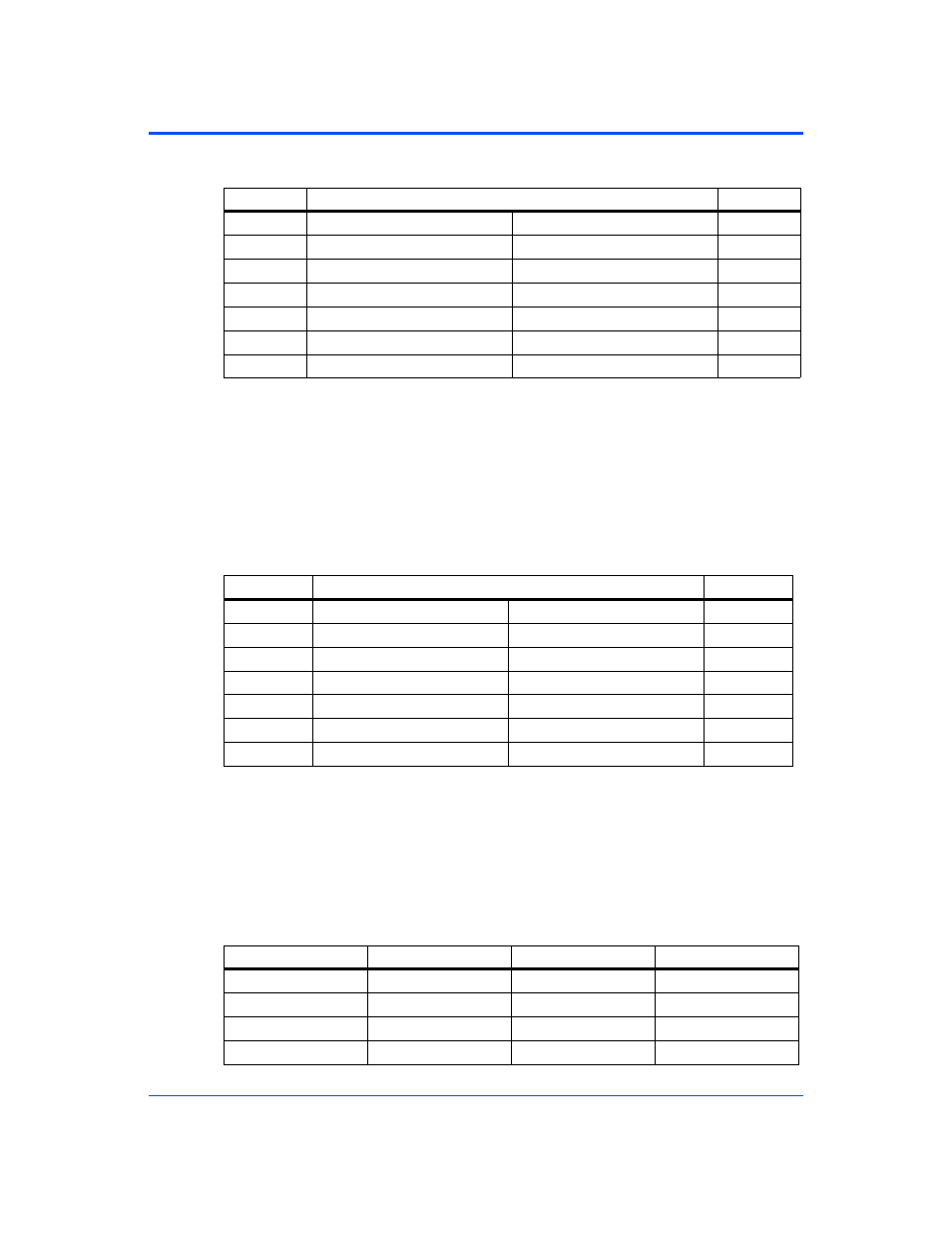

Boundary Scan JTAG Header

Controls, LEDs, and Connectors

CPCI-6115 CompactPCI Single Board Computer Installation and Use (6806800A68D)

63

3.5.10

Boundary Scan JTAG Header

This 2x7 0.1" header is used to provide boundary scan testing of all onboard JTAG devices in

a single scan chain. The pin assignments for this header are as follows:

J16 pin 12 is grounded in the JTAG test cable. When the cable is attached, the CPU_BSCAN_L

signal is grounded, which automatically configures the boundary scan chain to include the CPU.

3.5.11

Processor JTAG/COP Header

The processor has a 2x8 0.1" JTAG/COP header for use with third party MPC745x JTAG/COP

controllers. The pin assignments for this header are as follows:

With no JTAG cable attached to J16, the CPU JTAG signals are routed to J17 as shown.

51

PMCIO51

PMCIO52

52

53

PMCIO53

PMCIO54

54

55

PMCIO55

PMCIO56

56

57

PMCIO57

PMCIO58

58

59

PMCIO59

PMCIO60

60

61

PMCIO61

PMCIO62

62

63

PMCIO63

PMCIO64

64

Table 3-11 PMC Connector Pin Assignments , J14/J24 (continued)

Pin

J14/J24

Pin

Table 3-12 Boundary Scan JTAG Header Pin Assignments, J16

Pin

Signal

Pin

1

TRST_L

GND

2

3

TDO

GND

4

5

TDI

GND

6

7

TMS

GND

8

9

TCK

GND

10

11

NC

CPU_BSCAN_L

12

13

AUTOWR_L

GND

14

Table 3-13 Processor JTAG/COP Header Pin Assignments, J17

Pin

Signal

Pin

Signal

1

CPUTDO

2

QACK_L

3

CPUTDI

4

CPUTRST_L

5

QREQ_L

6

+1.8 V

7

CPUTCK

8

CHKSTPI_L