14 board reset logic, 15 mv64360 mpp configuration, Table 4-2 – Motorola CPCI-6115 User Manual

Page 77: Mv64360 mpp pin function assignments

MV64360 System Controller

Functional Description

CPCI-6115 CompactPCI Single Board Computer Installation and Use (6806800A68D)

75

4.3.4.14 Board Reset Logic

The board reset logic is implemented in a programmable logic device (PLD) in order to provide

maximum flexibility of the circuit. Refer to

potential reset sources.

4.3.4.15 MV64360 MPP Configuration

The MV64360 contains a 32-bit multi-purpose port (MPP). The MPP pins can be configured as

general purpose I/O pins, as external interrupt inputs, or as specific control/status pins for one

of the MV64360 internal devices. After reset, all MPP pins default to general purpose inputs.

Software must then configure each of the pins for the desired function. The following table

defines the function assigned to each MPP pin on the CPCI-6115 board.

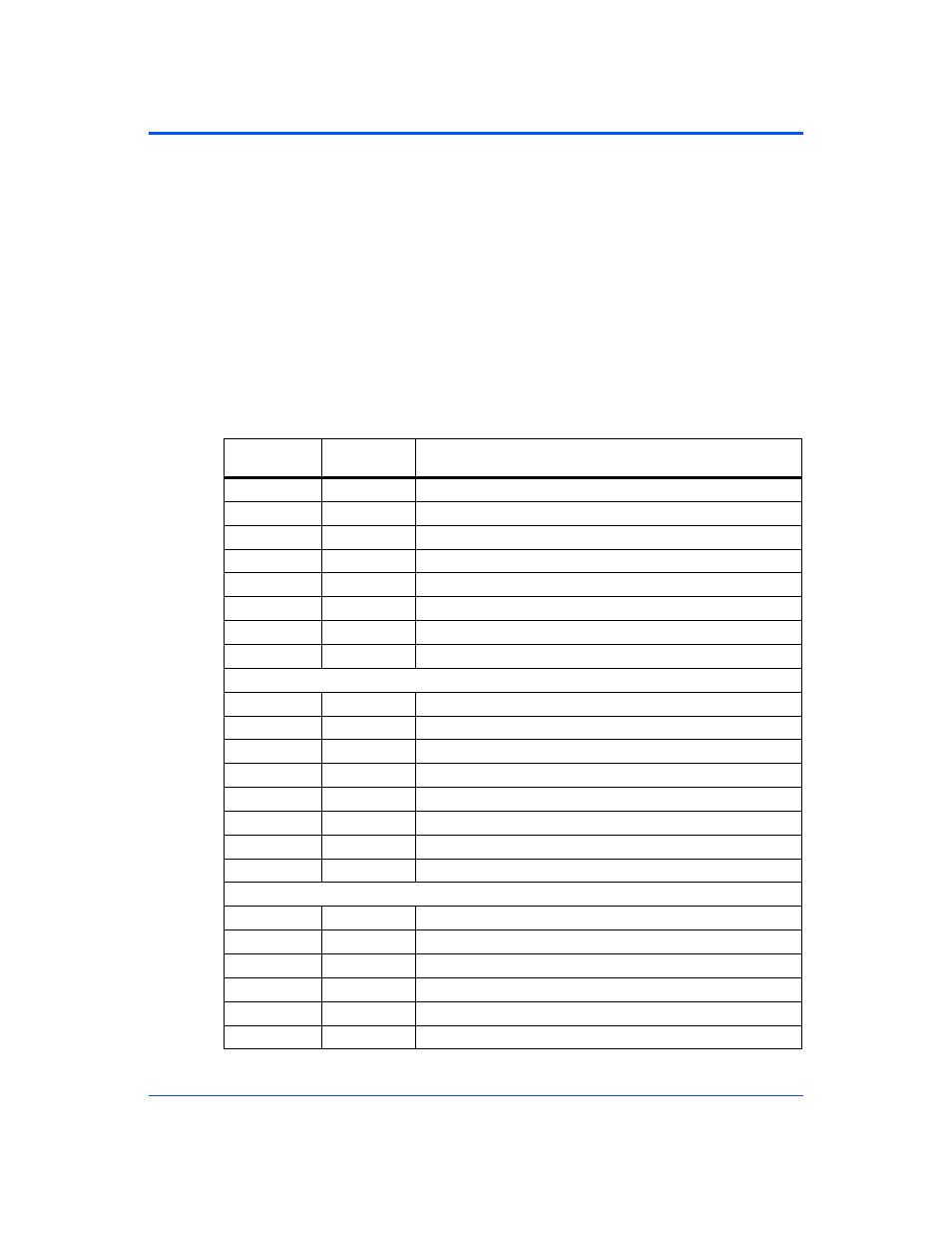

Table 4-2 MV64360 MPP Pin Function Assignments

MPP Pin

Number

Input/Output

Function

0

I

COM1 /COM2 interrupts (ORed)

1

I

Unused (optionally 21555 interrupt can be routed here)

2

I

Abort interrupt

3

I

RTC and Temperature Sensor interrupts (ORed)

4

I

Unused

5

I

Unused

6

I

MV64360 WDNMI# interrupt

7

I

BCM5421S PHY interrupts (ORed)

MPP[7:0] Interrupts

8

O

PCI Bus 1.0 - 21555 Bridge grant

9

I

PCI Bus 1.0 - 21555 Bridge request

10

O

PCI Bus 1.0 - PMC 1 secondary grant (GNTB#)

11

I

PCI Bus 1.0 - PMC 1 secondary request (REQB#)

12

O

PCI Bus 1.0 - PCI646U2 IDE Controller grant

13

I

PCI Bus 1.0 - PCI646U2 IDE Controller request

14

O

PCI Bus 1.0 - PMC 1 grant

15

I

PCI Bus 1.0 - PMC 1 request

MPP[15:8] PCI_1 Arbitration Request-Grant Pairs

16

I

PCI Bus 1.0 Interrupts - PMC1 INTA#, PMC1 INTC#, 21555

17

I

PCI Bus 1.0 Interrupts - PMC1 INTB#, PMC1 INTD#, IDE

18

I

PCI Bus 0.0 Interrupts - PMC2 INTA#, PMC2 INTC#

19

I

PCI Bus 0.0 Interrupts - PMC2 INTB#, PMC2 INTD#

20

I

CompactPCI Bus Interrupts - INTA#

21

I

CompactPCI Bus Interrupts - INTB#