5 system i/o memory map, 6 pci local bus memory map, 7 compactpci memory map – Motorola CPCI-6115 User Manual

Page 131: System i/o memory map, Pci local bus memory map, Compactpci memory map, Table 8-5, Device bank 1 i/o memory map

System I/O Memory Map

Memory Maps

CPCI-6115 CompactPCI Single Board Computer Installation and Use (6806800A68D)

129

8.2.5

System I/O Memory Map

System resources including system control and status registers, NVRAM/RTC and the 16550

UART are mapped into a 1 MB address range assigned to Device Bank 1. The memory map is

defined in the following table:

All register descriptions follow a fixed convention. The possible operations for each bit within a

register are as follows:

R - The bit is a read only status bit.

R/W - The bit is readable and writable.

R/C - The bit is cleared by writing a one to itself.

W - The bit is a write only bit.

8.2.6

PCI Local Bus Memory Map

There are two PCI local buses on the CPCI-6115: PCI Bus 0.0 and PCI Bus 1.0. The only device

on PCI Bus 0.0 is PMC 2. The PCI devices on PCI Bus 1.0 are PMC 1, the CMD 646U2 IDE

controller and the Intel 21555 PCI-to-PCI bridge.

8.2.7

CompactPCI Memory Map

The CPCI-6115 uses the 21555 non-transparent PCI-to-PCI bridge to interface between the

local PCI bus and the CompactPCI bus. The 21555 is different from traditional PCI-to-PCI

bridges in that it uses address translation instead of a flat address map between primary and

secondary PCI buses. In the CPCI-6115 configuration, the primary bus is the CompactPCI bus

and the secondary bus is the CPCI-6115 local bus. Downstream transactions are those that are

initiated on the primary bus and are forwarded to the secondary bus. Upstream transactions are

those initiated on the secondary bus and forwarded to the primary bus.

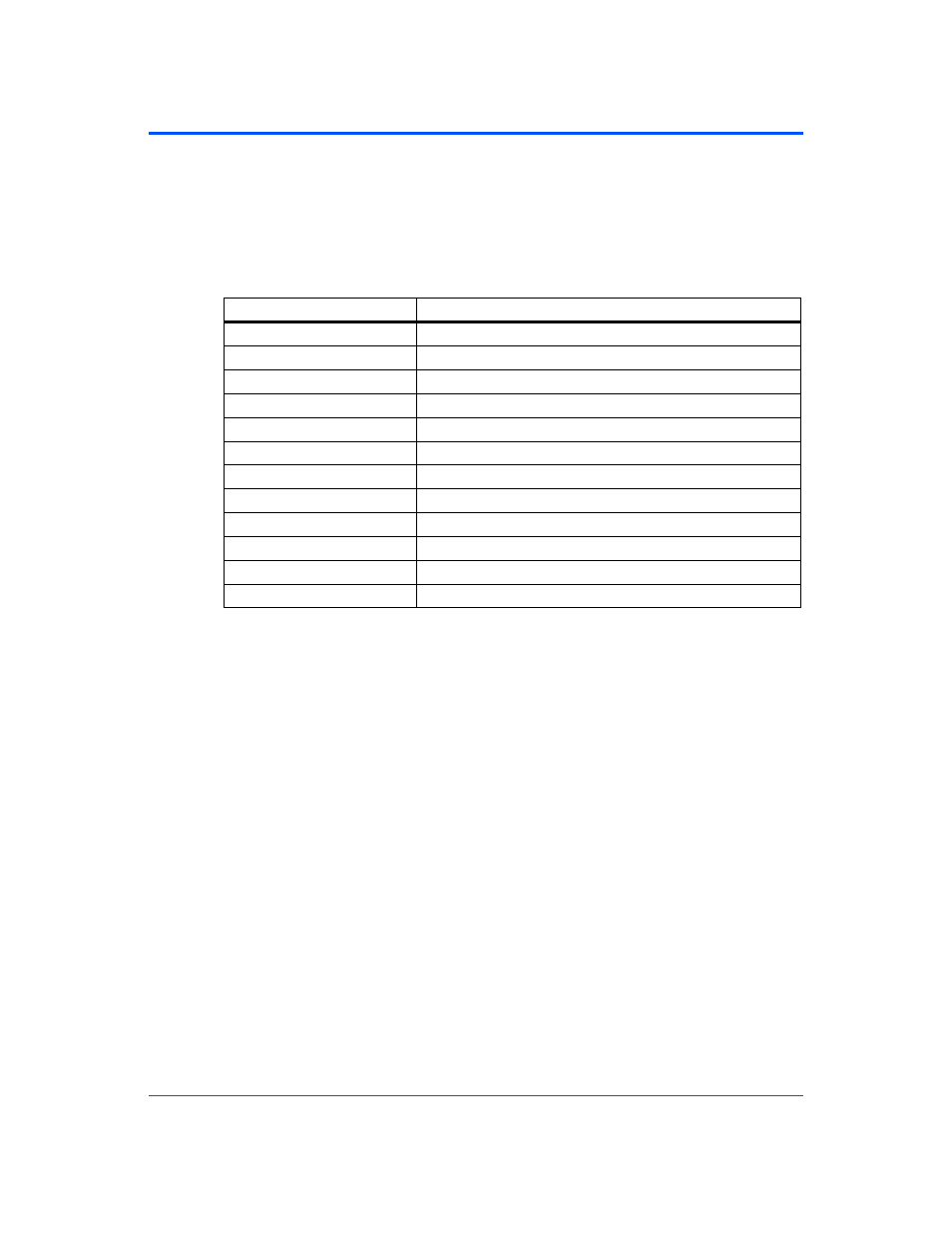

Table 8-5 Device Bank 1 I/O Memory Map

Address

Definition

F110 0000

System Control/Status Register 1

F110 0001

System Control/Status Register 2

F110 0002

System Control/Status Register 3

F110 0003

Geographic Address Register (CompactPCI)

F110 0004

PCI Presence Detect Register

F110 0005

Software Readable Header/Switch

F110 0006

Timebase Enable Register

F110 0008

System Interrupt Status Register

F110 0009 - F110 FFFF

Reserved for onboard registers

F111 0000 - FF11 7FFF

M48T37V NVRAM/RTC

F112 0000 - FF12 0FFF

COM1 16550 UART

F112 1000 - FF12 1FFF

COM2 16550 UART