Figure 5-6, P2mx signal timings – Motorola CPCI-6115 User Manual

Page 108

CPCI-6115 CompactPCI Single Board Computer Installation and Use (6806800A68D)

Transition Module Preparation and Installation

Asynchronous Serial Ports

106

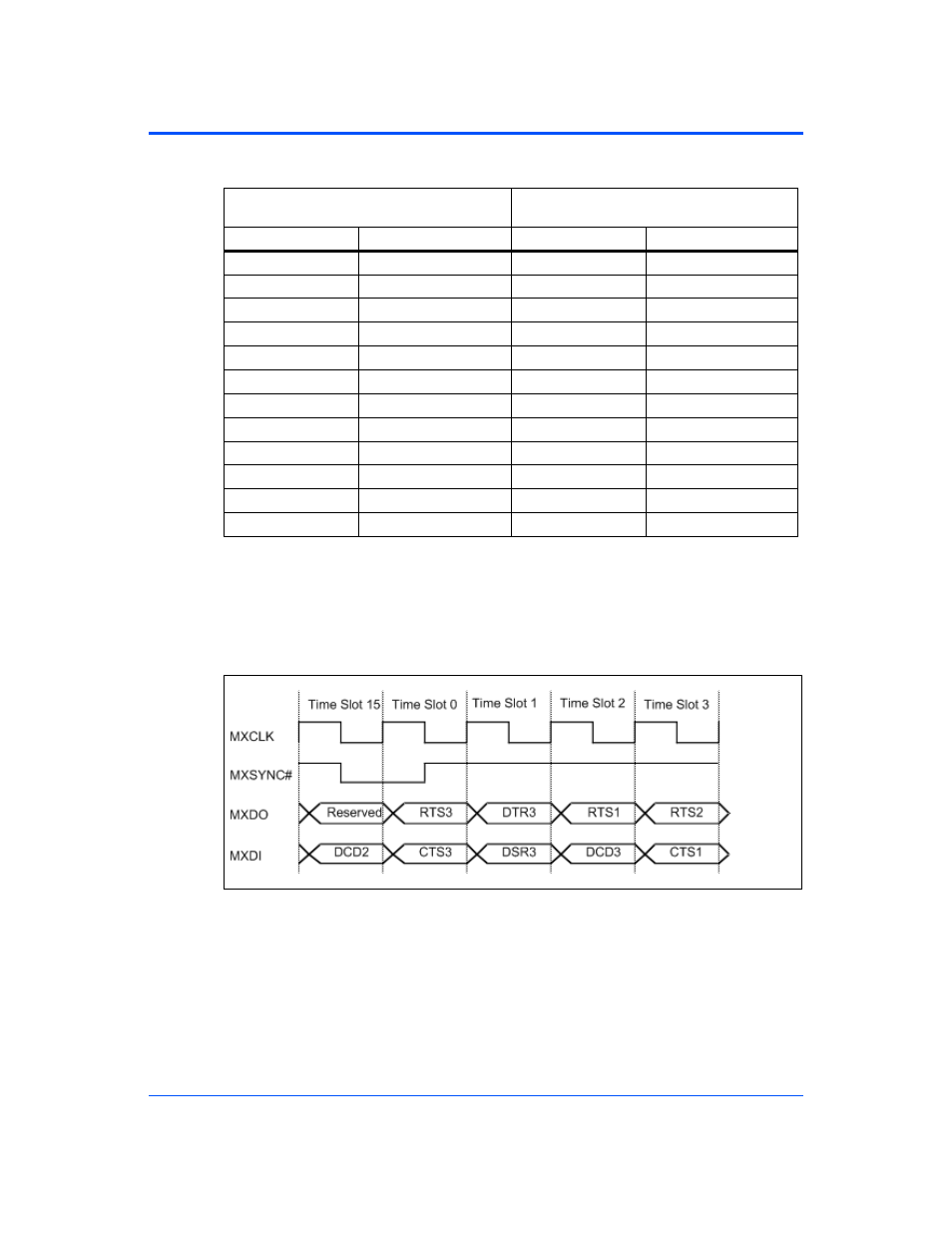

MXSYNC# is clocked out using the falling edge of MXCLK and MDXO is clocked out with the

rising edge of the MXCLK. MXDI is sampled at the rising edge of MXCLK (the CPCI-6115-

MCPTM synchronizes MXDI with MXCLK’s rising edge). The timing relationships among

MXCLK, MXSYNC#, MXDO, and MXDI are illustrated by the following figure:

4

RTS4

4

RI3

5

DTR4

5

CTS4

6

Reserved

6

DSR4

7

Reserved

7

DCD4

8

Reserved

8

CTS2

9

DTR1

9

RI4

10

DTR2

10

RI1

11

Reserved

11

DSR1

12

Reserved

12

DCD1

13

Reserved

13

RI2

14

Reserved

14

DSR2

15

Reserved

15

DCD2

Figure 5-6

P2MX Signal Timings

Serial Port Signal Descriptions

CTSn

clear to send

DCDn

data carrier detected

DSRn

data set ready

DTRn

data terminal ready

Table 5-12 Multiplexing Sequence of the IOMX Function (continued)

MXDO

(From CPCI-6115 SBC)

MXDI

(From CPCI-6115-MCPTM or CPCI-6106)

Time Slot

Signal Name

Time Slot

Signal Name