2 processor memory map, Processor memory map – Motorola CPCI-6115 User Manual

Page 128

CPCI-6115 CompactPCI Single Board Computer Installation and Use (6806800A68D)

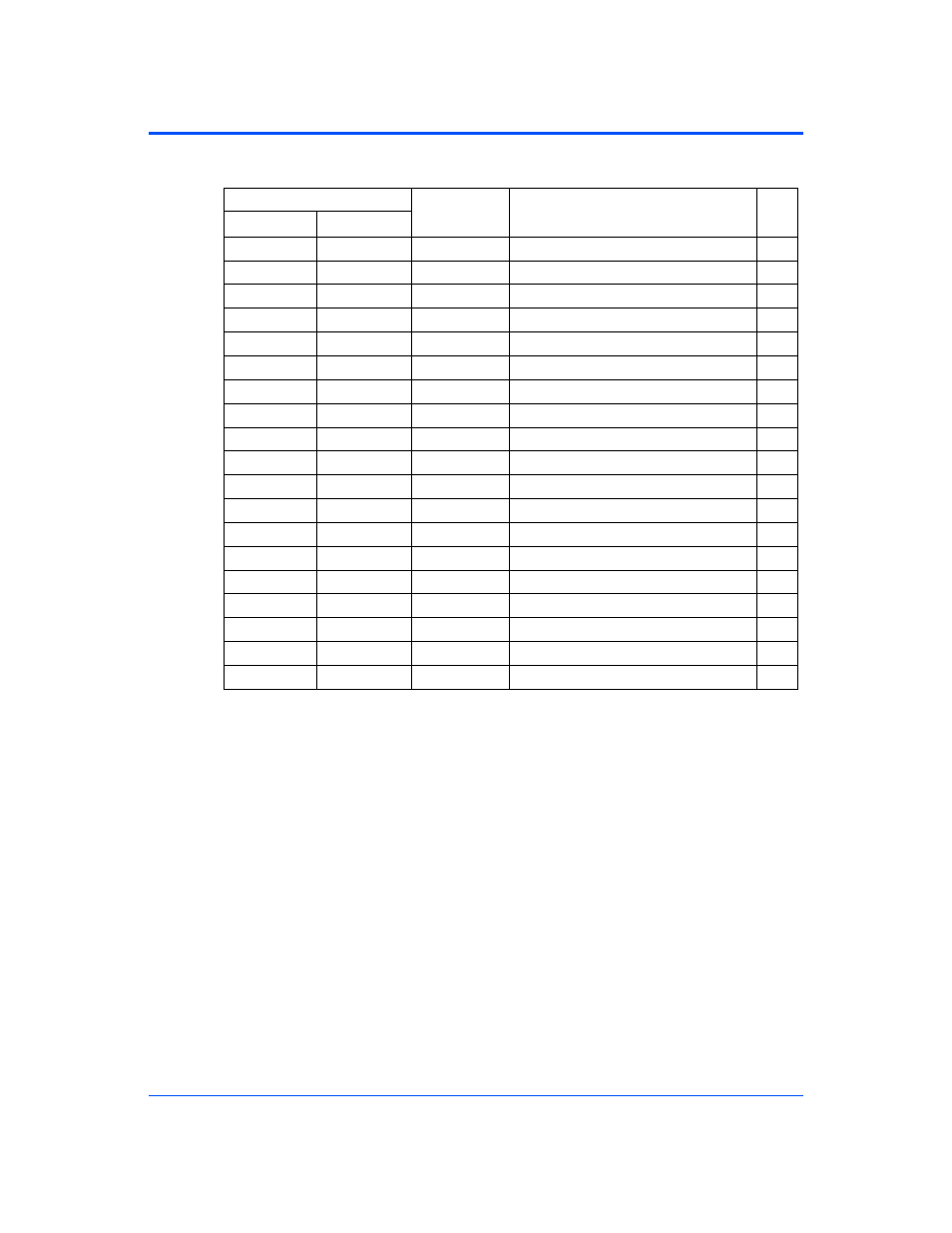

Memory Maps

Processor Memory Map

126

1.Set by configuration resistors.

2.This may be Flash Bank A or B, depending on the setting of the Flash Boot Bank Select

jumper.

8.2.2

Processor Memory Map

The following table describes a suggested Memory Map from the point of view of the Processor.

The beginning of PCI Memory Space is determined by the end of DRAM rounded up to the

nearest 256 MB boundary. For example, if memory was 1G on the baseboard and 192 MB on

a mezzanine, the beginning of PCI memory would be rounded up to address 0x50000000 (1

GB + 256 MB).

1C80 0000

1CFF FFFF

8 MB

Device CS1*

1D00 0000

1DFF FFFF

16 MB

Device CS2*

1E00 0000

1FFF FFFF

32 MB

Unassigned

2000 0000

21FF FFFF

32 MB

PCI Bus 1 I/O

2200 0000

23FF FFFF

32 MB

PCI Bus 1 Memory Space 0

2400 0000

25FF FFFF

32 MB

PCI Bus 1 Memory Space 1

2600 0000

27FF FFFF

32 MB

PCI Bus 1 Memory Space 2

2800 0000

29FF FFFF

32 MB

PCI Bus 1 Memory Space 3

2A00 0000

41FF FFFF

384 MB

Unassigned

4200 0000

4303 FFFF

256 KB

MV64360 Integrated SRAM

4304 0000

F0FF FFFF

2783 MB

Unassigned

F100 0000

F100 FFFF

64 KB Aliased

Internal Registers

1

F101 0000

F1FF FFFF

16 MB-64 KB

Unassigned

F200 0000

F3FF FFFF

32 MB

PCI Bus 0 Memory Space 1

F400 0000

F5FF FFFF

32 MB

PCI Bus 0 Memory Space 2

F600 0000

F7FF FFFF

32 MB

PCI Bus 0 Memory Space 3

F800 0000

FEFF FFFF

112 MB

Unassigned

FF00 0000

FF7F FFFF

8 MB

Device CS3*

FF80 0000

FFFF FFFF

8 MB

Boot Flash

2

Table 8-1 Default Processor Memory Map (continued)

Processor Address

Size

Definition

No

tes

Start

End