7 special programming exceptions, Special programming exceptions, Cgm numeric example – Freescale Semiconductor MC68HC08KH12 User Manual

Page 95

MC68HC(7)08KH12

—

Rev. 1.1

Advance Information

Freescale Semiconductor

95

2. Choose a practical PLL (crystal) reference frequency, f

RCLK

, and

the reference clock divider, R.

Frequency errors to the PLL are corrected at a rate of f

RCLK

/R. For

stability and lock time reduction, this rate must be as fast as

possible. The VCO frequency must be an integer multiple of this

rate. The relationship between the VCO frequency f

VCLK

and the

reference frequency f

RCLK

is

Choose the reference divider R = 1 for fast lock. Choose a f

RCLK

frequency with an integer divisor of f

BUS

and solve for N.

3. Program the PLL registers accordingly:

a.

In the PRE bits of the PLL control register (PCTL), program

the binary equivalent of P.

b.

In the PLL multiplier select register low (PMSL) and the PLL

multiplier select register high (PMSH), program the binary

equivalent of N.

c.

In the PLL reference divider select register (PRDS), program

the binary coded equivalent of R.

provides a numeric example (numbers are in hexadecimal

notation):

8.4.7 Special Programming Exceptions

The programming method described in

does not account for three possible exceptions. A value of zero for R, N,

or L is meaningless when used in the equations given. To account for

these exceptions:

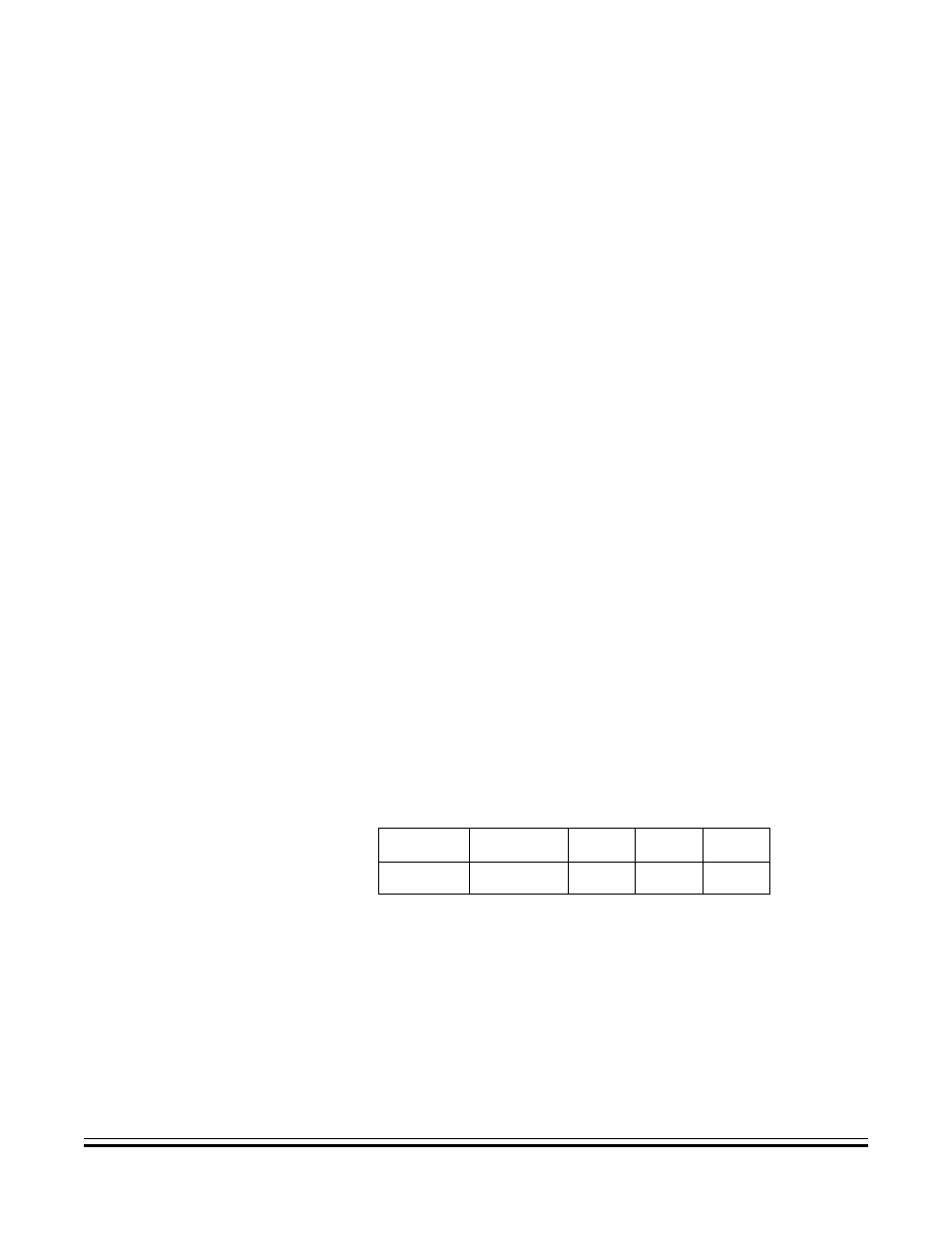

Table 8-1. CGM Numeric Example

f

BUS

f

RCLK

P

N

R

6MHz

6MHz

1

004

1

f

VCLK

2

P

N

×

R

-----------------

f

RCLK

(

)

=

hence: 48MHz

2

P

N

×

R

-----------------

f

RCLK

(

)

=