1 break status and control register (brkscr), 2 break address registers (brkh and brkl), Break status and control register (brkscr) – Freescale Semiconductor MC68HC08KH12 User Manual

Page 245: Break address registers (brkh and brkl)

MC68HC(7)08KH12

—

Rev. 1.1

Advance Information

Freescale Semiconductor

245

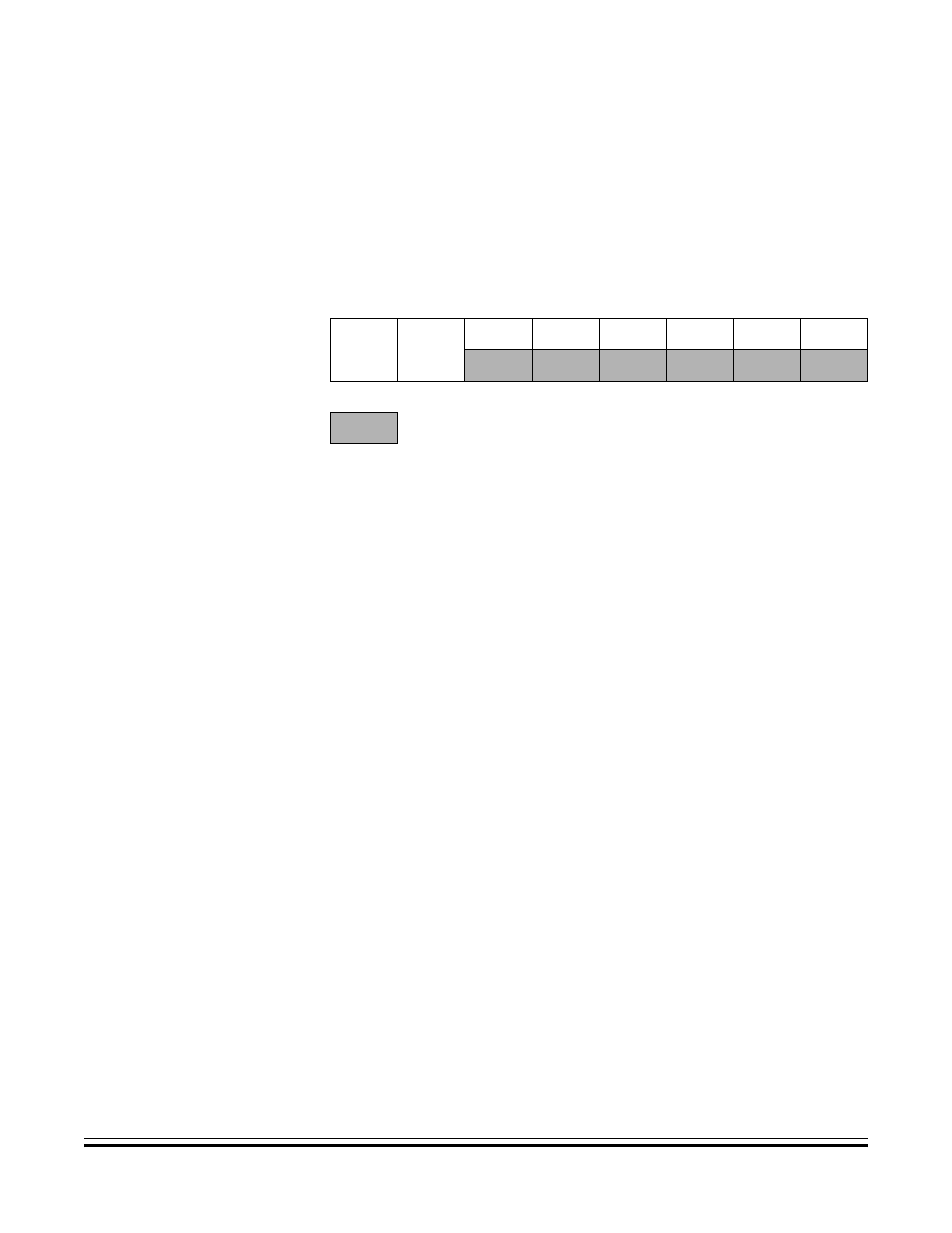

16.5.1 Break Status and Control Register (BRKSCR)

The break status and control register contains break module enable and

status bits.

BRKE — Break Enable Bit

This read/write bit enables breaks on break address register matches.

Clear BRKE by writing a logic zero to bit 7. Reset clears the BRKE bit.

1 =

Breaks enabled on 16-bit address match

0 =

Breaks disabled

BRKA — Break Active Bit

This read/write status and control bit is set when a break address

match occurs. Writing a logic one to BRKA generates a break

interrupt. Clear BRKA by writing a logic zero to it before exiting the

break routine. Reset clears the BRKA bit.

1 =

Break address match

0 =

No break address match

16.5.2 Break Address Registers (BRKH and BRKL)

The break address registers contain the high and low bytes of the

desired breakpoint address. Reset clears the break address registers.

Address: $FE0E

Bit 7

6

5

4

3

2

1

Bit 0

Read:

BRKE

BRKA

0

0

0

0

0

0

Write:

Reset:

0

0

0

0

0

0

0

0

= Unimplemented

Figure 16-2. Break Status and Control Register (BRKSCR)