5 usb embedded device control register 1 (dcr1), Usb embedded device control register 1 (dcr1) – Freescale Semiconductor MC68HC08KH12 User Manual

Page 143

MC68HC(7)08KH12

—

Rev. 1.1

Advance Information

Freescale Semiconductor

143

TP0SIZ3-TP0SIZ0 — Embedded Device Endpoint 0 Transmit Data

Packet Size

These read/write bits store the number of transmit data bytes for the

next IN token request for embedded device Endpoint 0. These bits are

cleared by reset.

9.5.5 USB Embedded Device Control Register 1 (DCR1)

T1SEQ — Embedded Device Endpoint 1/2 Transmit Sequence Bit

This read/write bit determines which type of data packet (DATA0 or

DATA1) will be sent during the next IN transaction directed to

embedded device Endpoint 1 or 2. Toggling of this bit must be

controlled by software. Reset clears this bit.

1 = DATA1 Token active for next embedded device Endpoint 1/2

transmit

0 = DATA0 Token active for next embedded device Endpoint 1/2

transmit

ENDADD — Endpoint Address Select

This read/write bit specifies whether the data inside the registers

DE1D0-DE1D7 are used for embedded device Endpoint 1 or 2. If all

the conditions for a successful Endpoint 2 USB response to a host’s

IN token are satisfied (TXD1F=0, TX1E=1, DSTALL2=0, and

ENABLE2=1) except that the ENDADD bit is configured for

Endpoint 1, the USB responds with a NAK handshake packet. Reset

clears this bit.

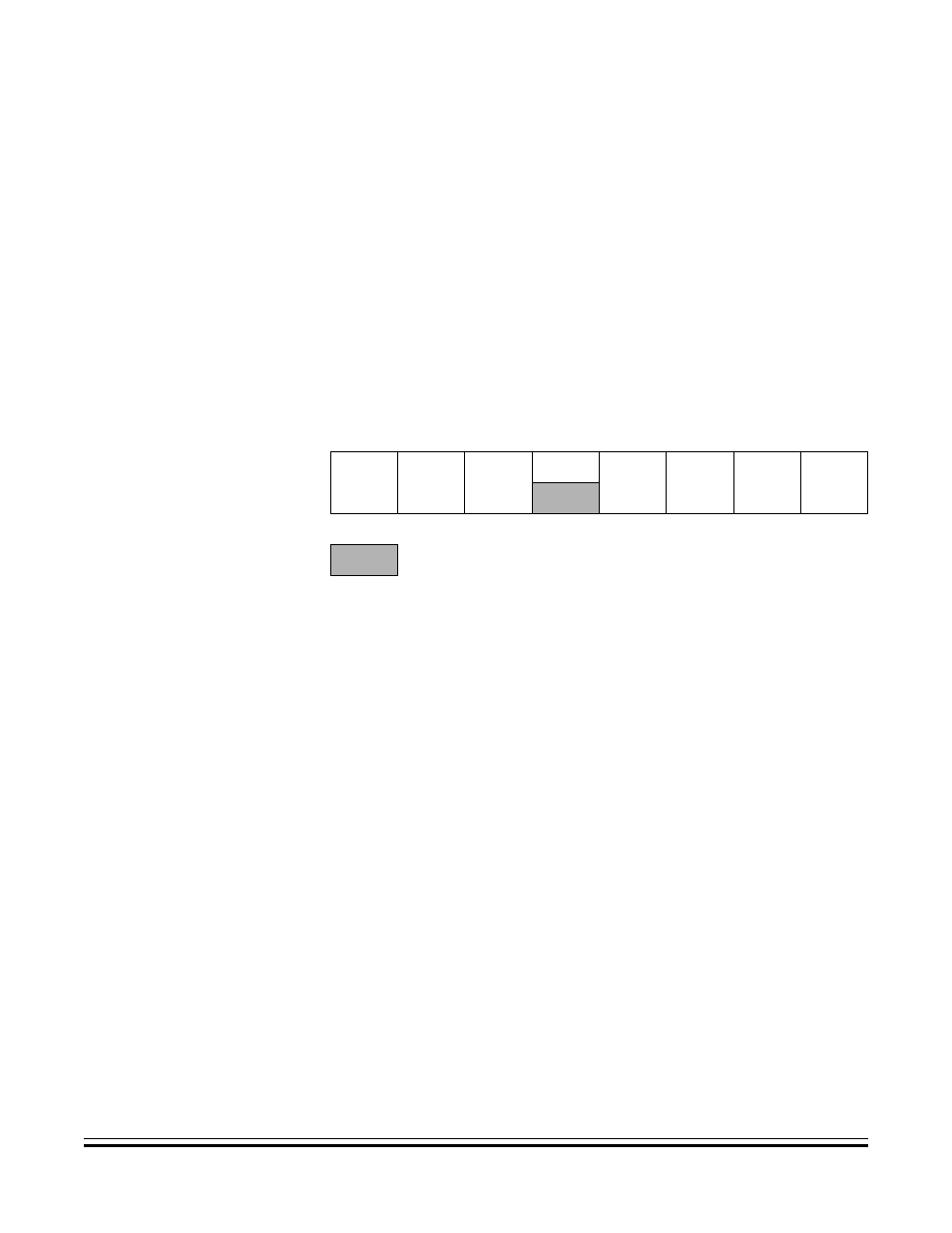

Address:

$004C

Bit 7

6

5

4

3

2

1

Bit 0

Read:

T1SEQ

ENDADD

TX1E

0

TP1SIZ3 TP1SIZ2 TP1SIZ1 TP1SIZ0

Write:

Reset:

0

0

0

0

0

0

0

0

= Unimplemented

Figure 9-16. USB Embedded Device Control Register 1 (DCR1)