3 break flag control register (bfcr), Break flag control register (bfcr) – Freescale Semiconductor MC68HC08KH12 User Manual

Page 85

MC68HC(7)08KH12

—

Rev. 1.1

Advance Information

Freescale Semiconductor

85

POR — Power-On Reset Bit

1 = Last reset caused by POR circuit

0 = Read of RSR

PIN — External Reset Bit

1 = Last reset caused by external reset pin (RST)

0 = POR or read of RSR

COP — Computer Operating Properly Reset Bit

1 = Last reset caused by COP counter

0 = POR or read of RSR

ILOP — Illegal Opcode Reset Bit

1 = Last reset caused by an illegal opcode

0 = POR or read of RSR

ILAD — Illegal Address Reset Bit (opcode fetches only)

1 = Last reset caused by an opcode fetch from an illegal

address

0 = POR or read of RSR

USB —Universal Serial Bus Reset Bit

1 = Last reset caused by an USB module

0 = POR or read of RSR

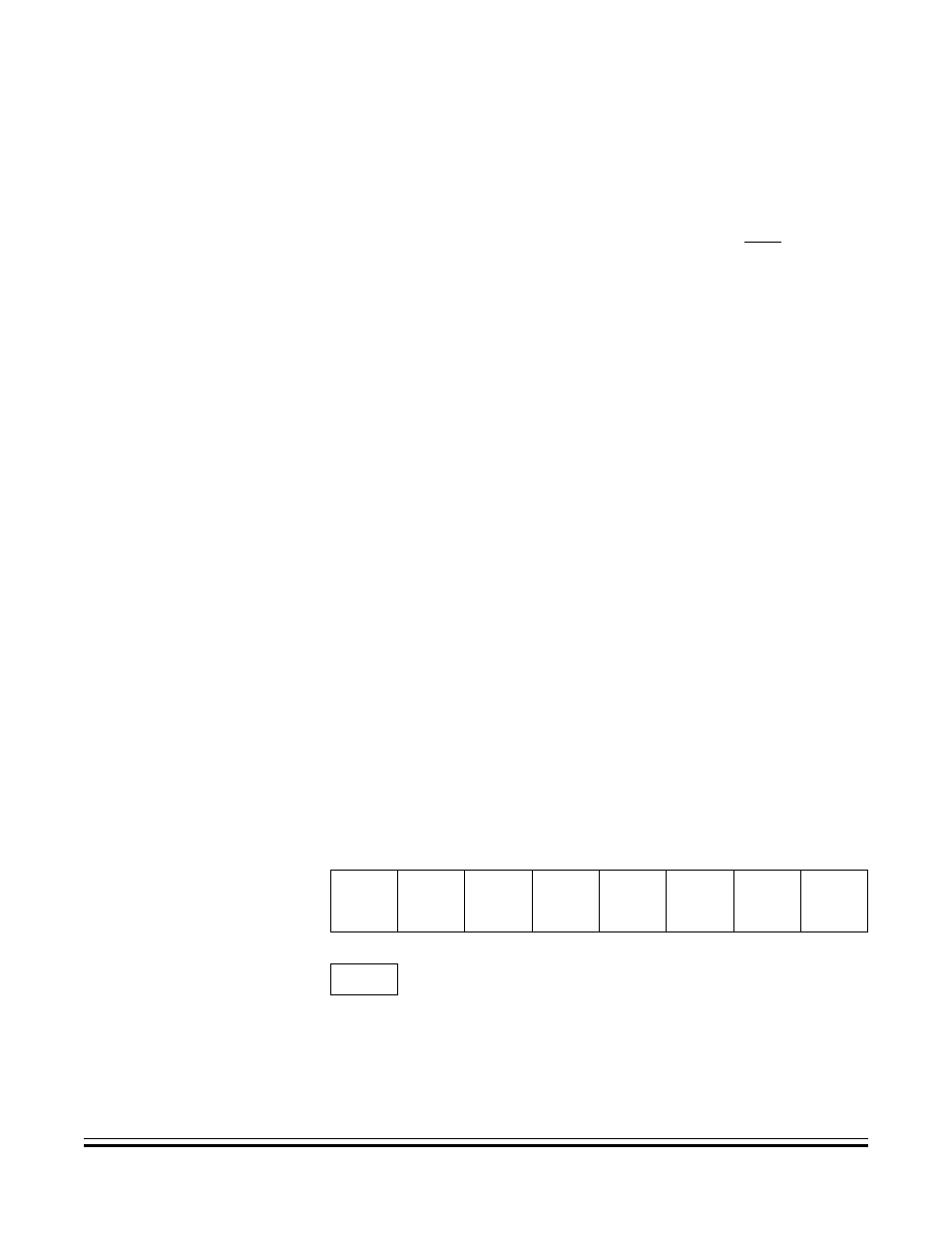

7.8.3 Break Flag Control Register (BFCR)

The break control register contains a bit that enables software to clear

status bits while the MCU is in a break state.

Address:

$FE03

Bit 7

6

5

4

3

2

1

Bit 0

Read:

BCFE

R

R

R

R

R

R

R

Write:

Reset:

0

0

0

0

0

0

0

0

R

= Reserved

Figure 7-22. Break Flag Control Register (BFCR)