3 tim counter modulo registers (tmodh:tmodl), Tim counter modulo registers (tmodh:tmodl), Tim counter registers (tcnth:tcntl) – Freescale Semiconductor MC68HC08KH12 User Manual

Page 176

Advance Information

MC68HC(7)08KH12

—

Rev. 1.1

176

Freescale Semiconductor

TCNTH do not affect the latched TCNTL value until TCNTL is read.

Reset clears the TIM counter registers. Setting the TIM reset bit (TRST)

also clears the TIM counter registers.

NOTE:

If you read TCNTH during a break interrupt, be sure to unlatch TCNTL

by reading TCNTL before exiting the break interrupt. Otherwise, TCNTL

retains the value latched during the break.

11.9.3 TIM Counter Modulo Registers (TMODH:TMODL)

The read/write TIM modulo registers contain the modulo value for the

TIM counter. When the TIM counter reaches the modulo value, the

overflow flag (TOF) becomes set, and the TIM counter resumes counting

from $0000 at the next clock. Writing to the high byte (TMODH) inhibits

the TOF bit and overflow interrupts until the low byte (TMODL) is written.

Reset sets the TIM counter modulo registers.

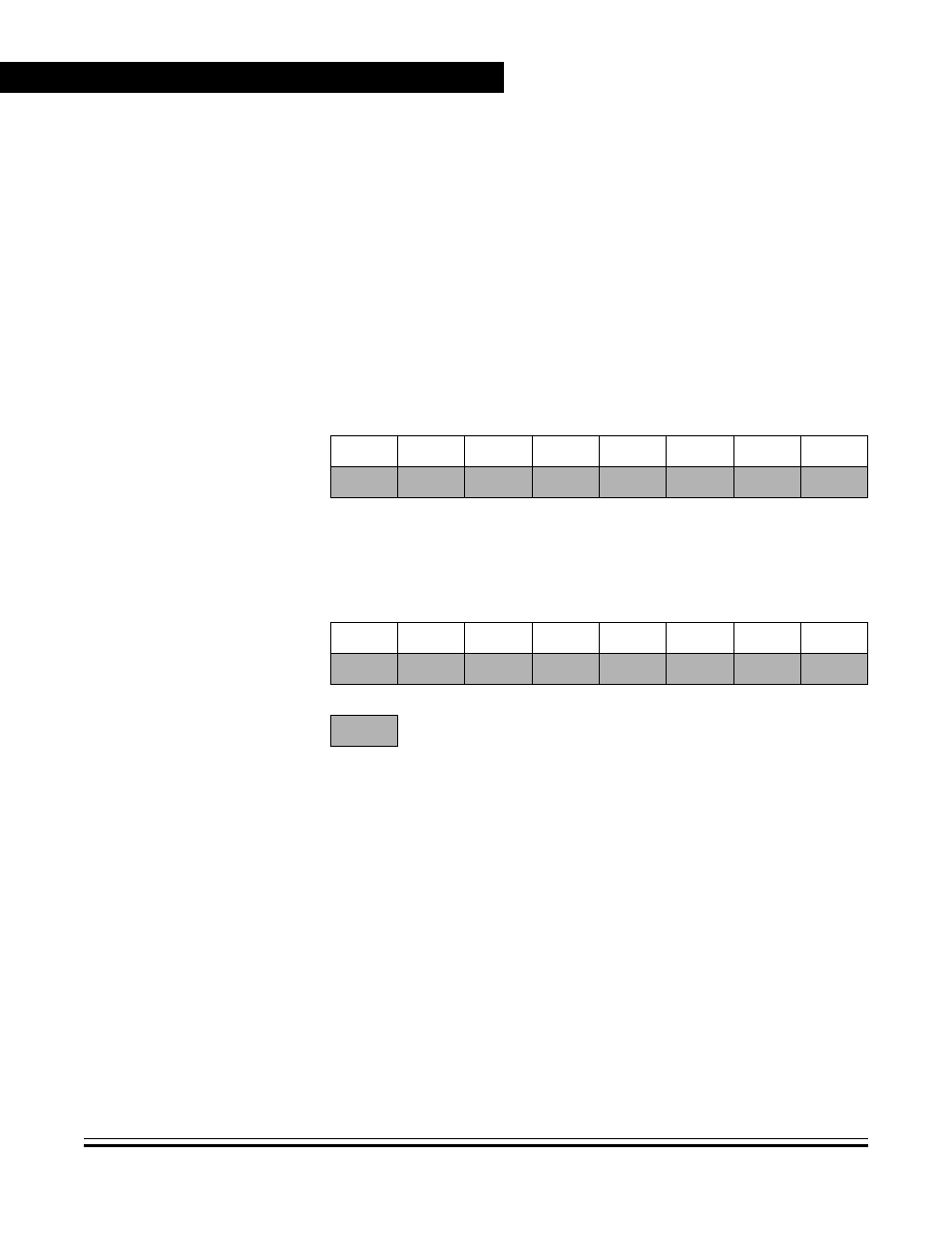

Address:

$0012

TCNTH

Bit 7

6

5

4

3

2

1

Bit 0

Read:

Bit15

Bit14

Bit13

Bit12

Bit11

Bit10

Bit9

Bit8

Write:

Reset:

0

0

0

0

0

0

0

0

Address:

$0013

TCNTL

Bit 7

6

5

4

3

2

1

Bit 0

Read:

Bit7

Bit6

Bit5

Bit4

Bit3

Bit2

Bit1

Bit0

Write:

Reset:

0

0

0

0

0

0

0

0

= Unimplemented

Figure 11-4. TIM Counter Registers (TCNTH:TCNTL)