3 port-e keyboard interrupt registers, 1 port-e keyboard status and control register, Port-e keyboard interrupt registers – Freescale Semiconductor MC68HC08KH12 User Manual

Page 231: Port-e keyboard status and control register

MC68HC(7)08KH12

—

Rev. 1.1

Advance Information

Freescale Semiconductor

231

4. Write to the ACKE bit in the keyboard status and control register

to clear any false interrupts.

5. Clear the IMASKE bit.

An interrupt signal on an edge-triggered pin can be acknowledged

immediately after enabling the pin. An interrupt signal on an edge- and

level-triggered interrupt pin must be acknowledged after a delay that

depends on the external load.

15.5.3 Port-E Keyboard Interrupt Registers

15.5.3.1 Port-E Keyboard Status and Control Register

•

Flags keyboard interrupt requests.

•

Acknowledges keyboard interrupt requests.

•

Masks keyboard interrupt requests.

•

Controls keyboard interrupt triggering sensitivity.

Bits [7:4] — Not used

These read-only bits always read as logic 0s.

KEYEF — Port-E Keyboard Flag Bit

This read-only bit is set when a keyboard interrupt is pending on

port-E. Reset clears the KEYEF bit.

1 = Keyboard interrupt pending

0 = No keyboard interrupt pending

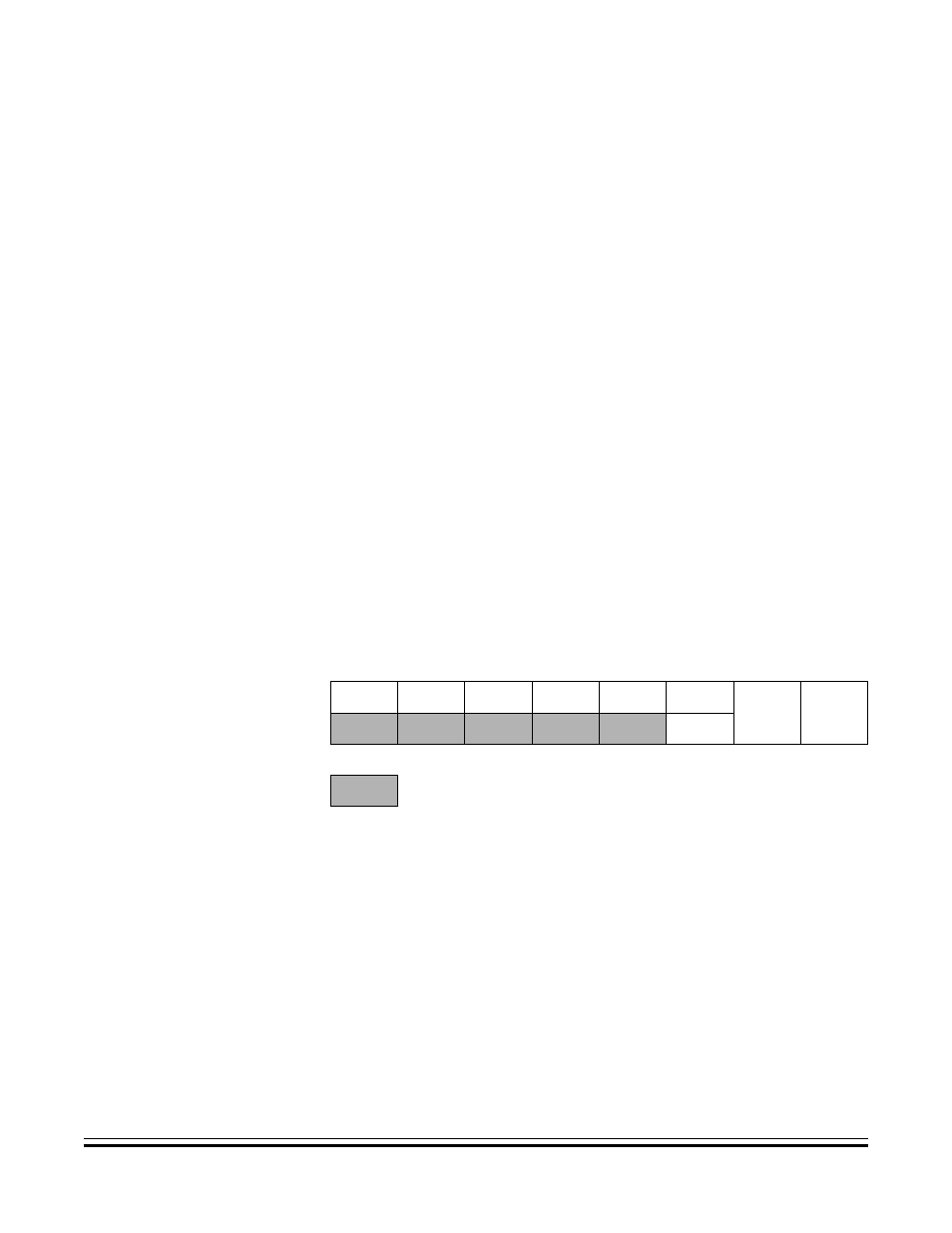

Address: $000E

Bit 7

6

5

4

3

2

1

Bit 0

Read:

0

0

0

0

KEYEF

0

IMASKE

MODEE

Write:

ACKE

Reset:

0

0

0

0

0

0

0

0

= Unimplemented

Figure 15-5. Port-E Keyboard Status and Control Register (KBESCR)