Freescale Semiconductor MC68HC08KH12 User Manual

Page 197

MC68HC(7)08KH12

—

Rev. 1.1

Advance Information

Freescale Semiconductor

197

DDRE[4:0] — Data Direction Register E Bits

These read/write bits control port E data direction. Reset clears

DDRE[4:0], configuring all port E pins as inputs.

1 = Corresponding port E pin configured as output

0 = Corresponding port E pin configured as input

NOTE:

Avoid glitches on port E pins by writing to the port E data register before

changing data direction register E bits from 0 to 1.

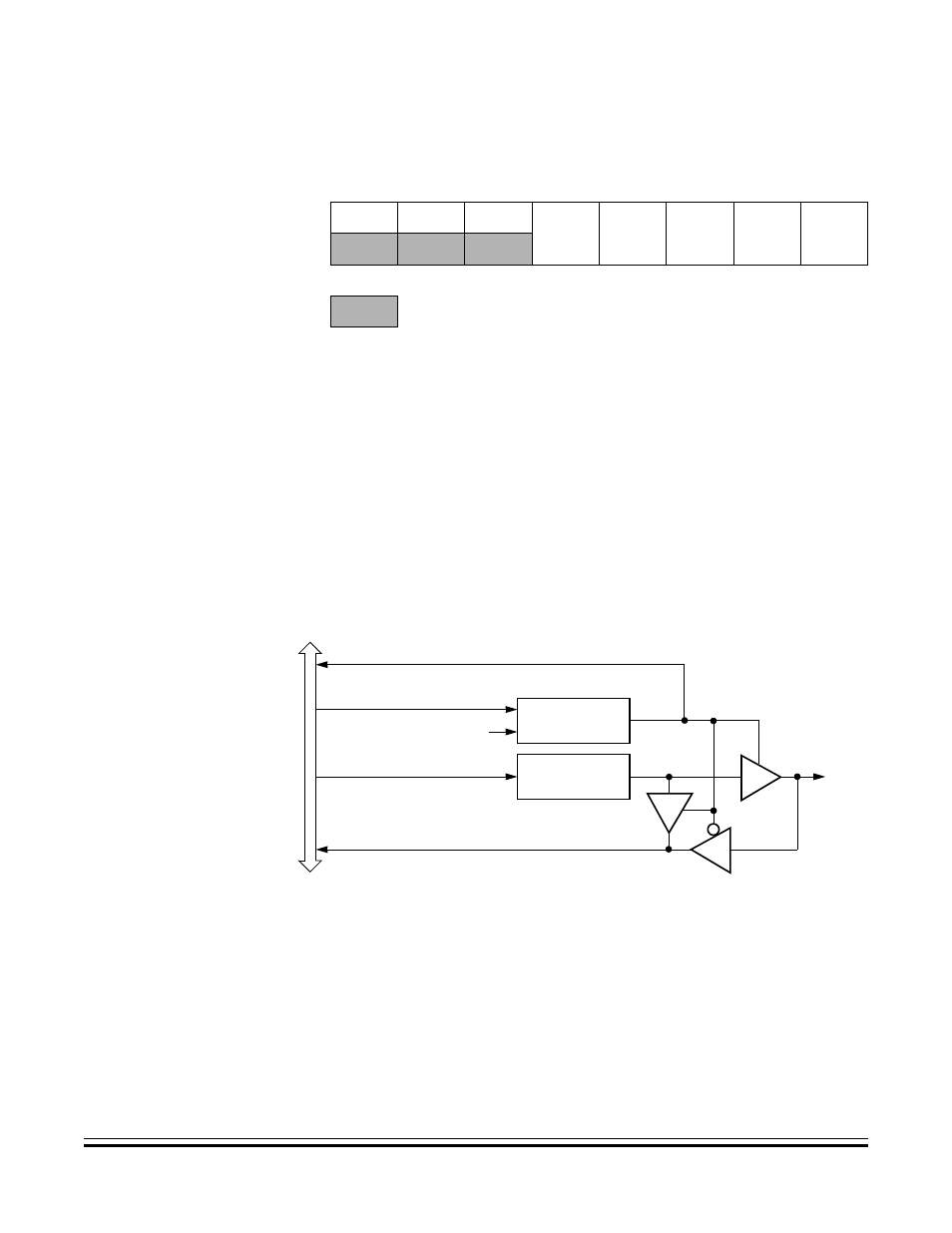

Figure 12-15. Port E I/O Circuit

When bit DDREx is a logic one, reading address $0008 reads the PTEx

data latch. When bit DDREx is a logic zero, reading address $0008

reads the voltage level on the pin. The data latch can always be written,

regardless of the state of its data direction bit.

summarizes

the operation of the port E pins.

Address:

$000A

Bit 7

6

5

4

3

2

1

Bit 0

Read:

0

0

0

DDRE4

DDRE3

DDRE2

DDRE1

DDRE0

Write:

Reset:

0

0

0

0

0

0

0

0

= Unimplemented

Figure 12-14. Data Direction Register E (DDRE)

READ DDRE ($000A)

WRITE DDRE ($000A)

RESET

WRITE PTE ($0008)

READ PTE ($0008)

PTEx

DDREx

PTEx

INT

ERNAL DATA BUS