2 pll bandwidth control register (pbwc), Pll bandwidth control register (pbwc), Pre[1:0] programming – Freescale Semiconductor MC68HC08KH12 User Manual

Page 104: 2 pll bandwidth control register, Pbwc), Bit (see, Is a read-only indi, 2 pll, Bandwidth control register (pbwc)

Advance Information

MC68HC(7)08KH12

—

Rev. 1.1

104

Freescale Semiconductor

8.6.2 PLL

Bandwidth Control Register (PBWC)

The PLL bandwidth control register:

•

Indicates when the PLL is locked

•

In automatic bandwidth control mode, indicates when the PLL is in

acquisition or tracking mode

AUTO — Automatic Bandwidth Control Bit

This read/write bit selects automatic or manual bandwidth control.

Since this CGM is optimized a frequency output of 48MHz for the USB

module, automatic control should be set. Reset clears the AUTO bit.

1 = Automatic bandwidth control (recommended)

0 = Manual bandwidth control

LOCK — Lock Indicator Bit

When the AUTO bit is set, LOCK is a read-only bit that becomes set

when the VCO clock, CGMVCLK, is locked (running at the

programmed frequency). When the AUTO bit is clear, LOCK reads as

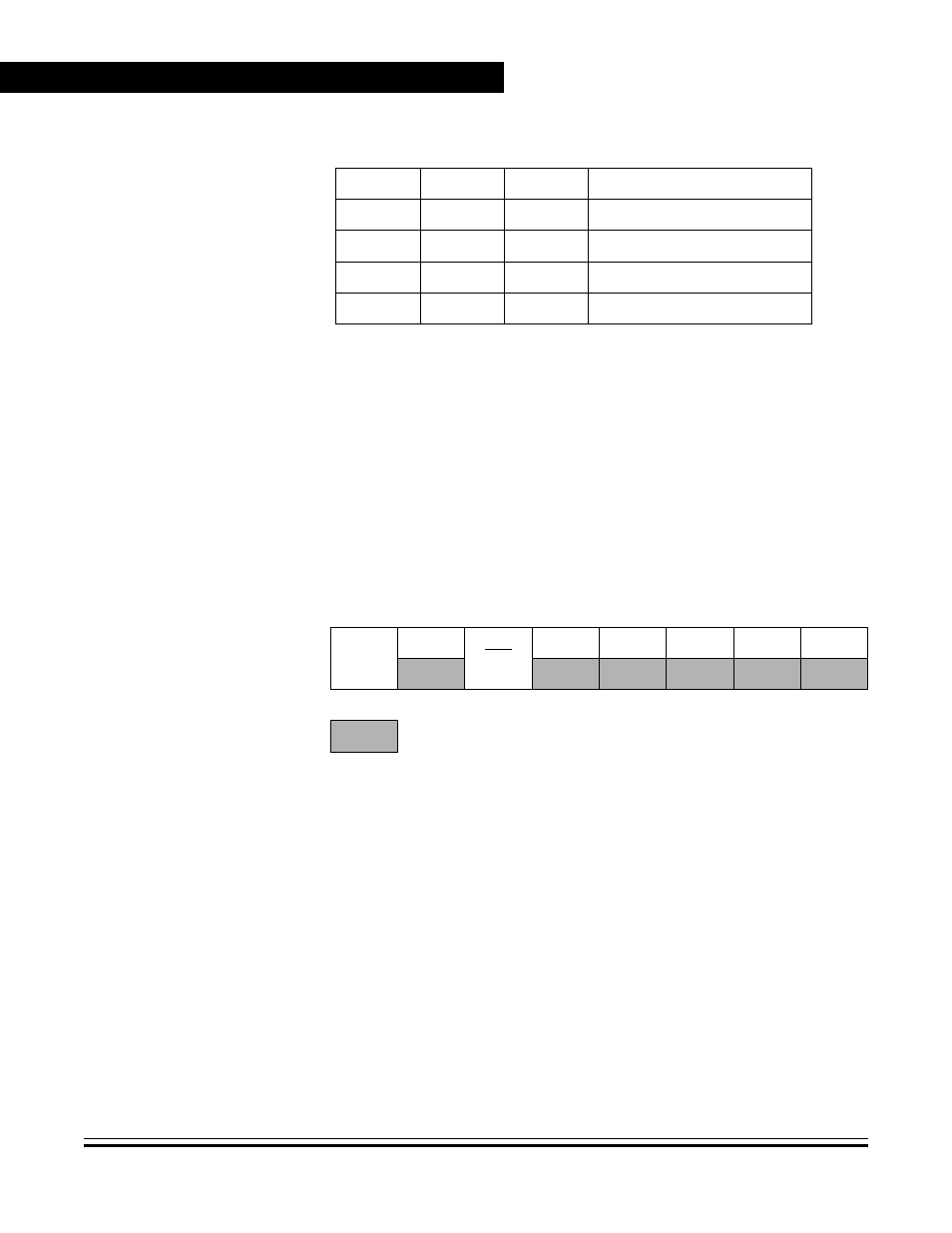

Table 8-3. PRE[1:0] Programming

PRE1

PRE0

P

Prescaler Multiplier

0

0

0

1

0

1

1

2

1

0

2

4

1

1

3

8

Address:

$003B

Bit 7

6

5

4

3

2

1

Bit 0

Read:

AUTO

LOCK

ACQ

0

0

0

0

0

Write:

Reset:

0

0

0

0

0

0

0

0

= Unimplemented

Figure 8-4. PLL Bandwidth Control Register (PBWC)