1 irq1/vpp pin, Irq module block diagram, Irq i/o port register summary – Freescale Semiconductor MC68HC08KH12 User Manual

Page 215: Figure 14-1, Pin a logic zero on the irq1/v, Table 14-1. irq i/o port register summary

MC68HC(7)08KH12

—

Rev. 1.1

Advance Information

Freescale Semiconductor

215

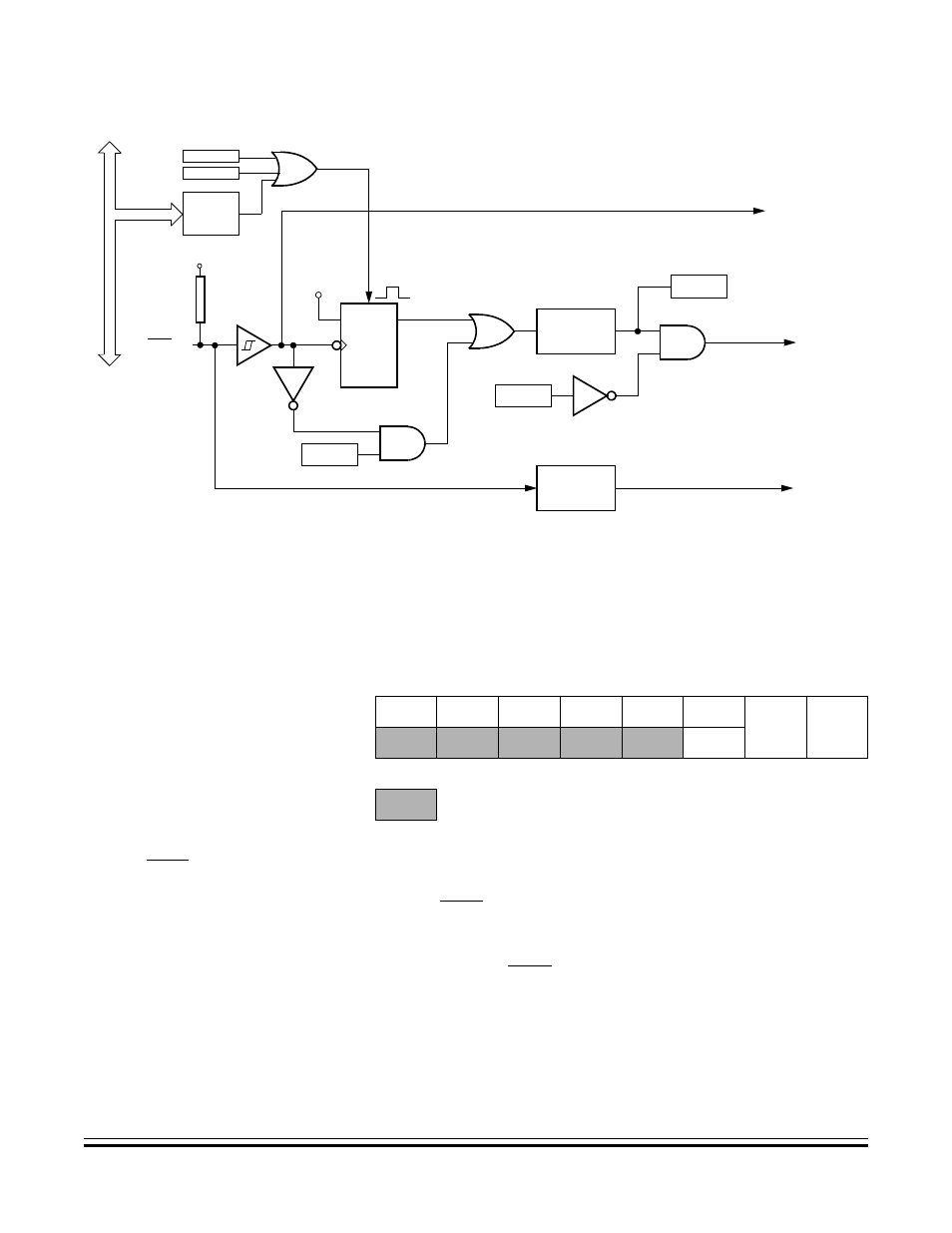

Figure 14-1. IRQ Module Block Diagram

14.4.1 IRQ1/V

PP

Pin

A logic zero on the IRQ1/V

PP

pin can latch an interrupt request into the

IRQ1 latch. A vector fetch, software clear, or reset clears the IRQ1 latch.

If the MODE1 bit is set, the IRQ1/V

PP

pin is both falling-edge-sensitive

and low-level-sensitive. With MODE1 set, both of the following actions

must occur to clear IRQ1:

ACK1

IMASK1

D

Q

CK

CLR

IRQ1

HIGH

INTERRUPT

TO MODE

SELECT

LOGIC

IRQ1

FF

REQUEST

IRQ1/V

PP

V

DD

MODE1

VOLTAGE

DETECT

SYNCHRO-

NIZER

IRQF1

TO CPU FOR

BIL/BIH

INSTRUCTIONS

VECTOR

FETCH

DECODER

INTERNAL

ADDR

ESS

BUS

RESET

V

DD

I

NTERNAL

PULLUP

DEVICE

Table 14-1. IRQ I/O Port Register Summary

Addr.

Register Name

Bit 7

6

5

4

3

2

1

Bit 0

$001E

IRQ Status/Control Register

(ISCR)

Read:

0

0

0

0

IRQF1

0

IMASK1 MODE1

Write:

ACK1

Reset:

0

0

0

0

0

0

0

0

= Unimplemented