5 irq module during break interrupts, 6 irq status and control register (iscr), Irq module during break interrupts – Freescale Semiconductor MC68HC08KH12 User Manual

Page 217: Irq status and control register (iscr)

MC68HC(7)08KH12

—

Rev. 1.1

Advance Information

Freescale Semiconductor

217

14.5 IRQ Module During Break Interrupts

The system integration module (SIM) controls whether the IRQ1 latch

can be cleared during the break state. The BCFE bit in the break flag

control register (BFCR) enables software to clear the latches during the

break state.

(See Section 7. System Integration Module (SIM)

To allow software to clear the IRQ1 latch during a break interrupt, write

a logic one to the BCFE bit. If a latch is cleared during the break state, it

remains cleared when the MCU exits the break state.

To protect the latches during the break state, write a logic zero to the

BCFE bit. With BCFE at logic zero (its default state), writing to the ACK1

bit in the IRQ status and control register during the break state has no

effect on the IRQ latch.

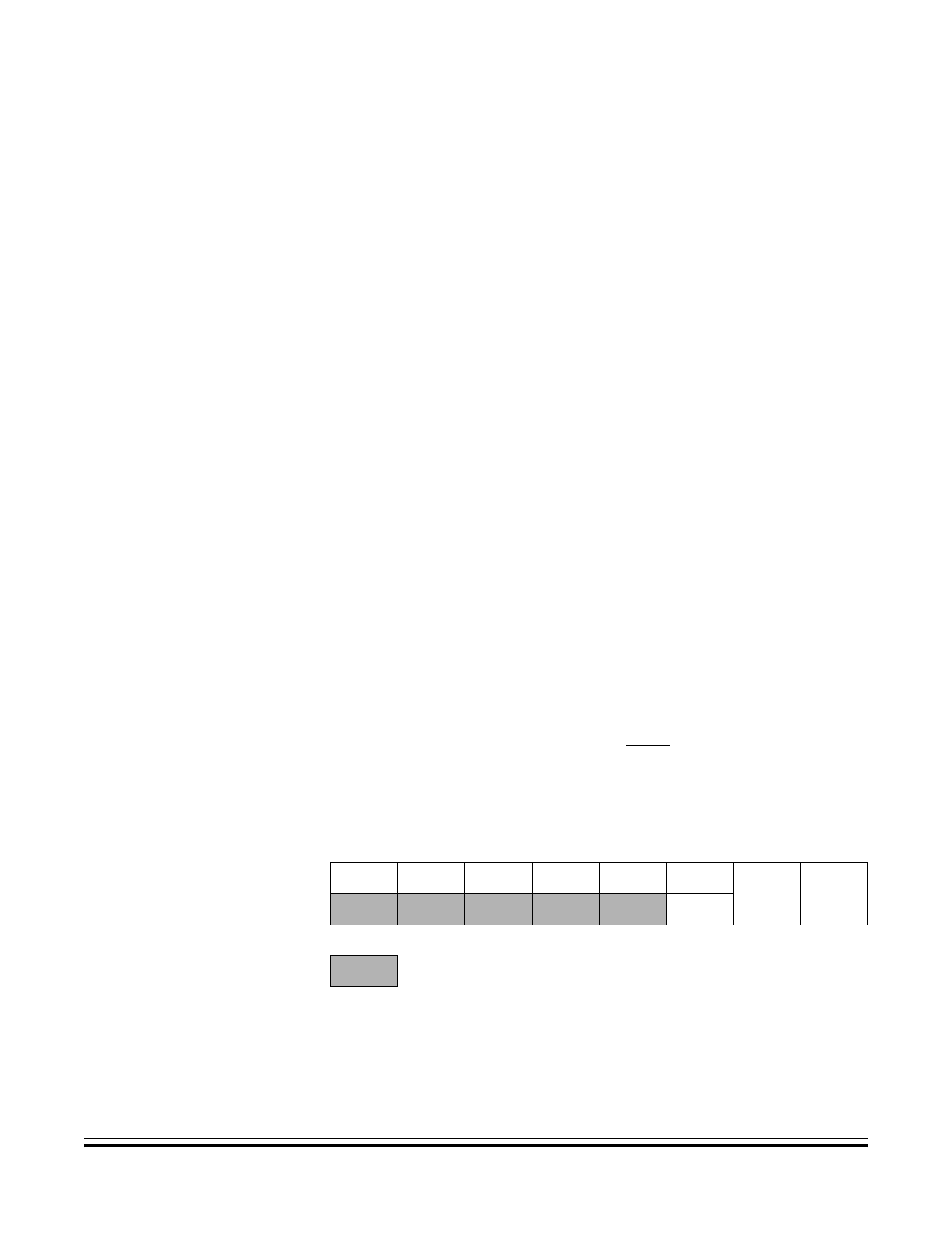

14.6 IRQ Status and Control Register (ISCR)

The IRQ Status and Control Register (ISCR) controls and monitors

operation of the IRQ module. The ISCR has the following functions:

•

Shows the state of the IRQ1 flag

•

Clears the IRQ1 latch

•

Masks IRQ1 and interrupt request

•

Controls triggering sensitivity of the IRQ1/V

PP

interrupt pin

Address:

$001E

Bit 7

6

5

4

3

2

1

Bit 0

Read:

0

0

0

0

IRQF1

0

IMASK1

MODE1

Write:

ACK1

Reset:

0

0

0

0

0

0

0

0

= Unimplemented

Figure 14-2. IRQ Status and Control Register (ISCR)