Freescale Semiconductor MC68HC08KH12 User Manual

Page 39

MC68HC(7)08KH12

—

Rev. 1.1

Advance Information

Freescale Semiconductor

39

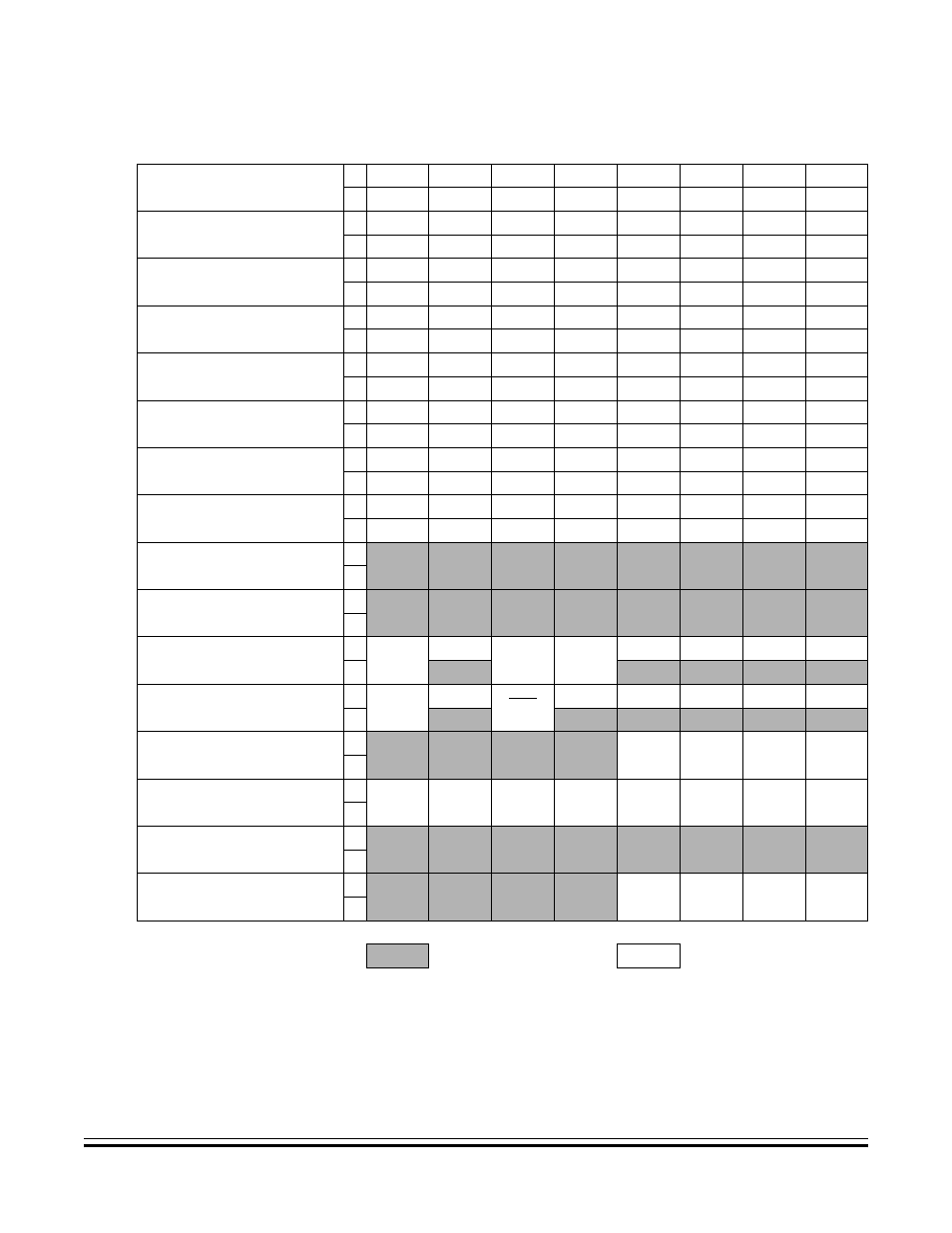

$0030

USB HUB Endpoint 0 Data

Register 0 (HE0D0)

R: HE0R07 HE0R06 HE0R05 HE0R04 HE0R03 HE0R02 HE0R01 HE0R00

W: HE0T07 HE0T06 HE0T05 HE0T04 HE0T03 HE0T02 HE0T01 HE0T00

$0031

USB HUB Endpoint 0 Data

Register 1 (HE0D1)

R: HE0R17 HE0R16 HE0R15 HE0R14 HE0R13 HE0R12 HE0R11 HE0R10

W: HE0T17 HE0T16 HE0T15 HE0T14 HE0T13 HE0T12 HE0T11 HE0T10

$0032

USB HUB Endpoint 0 Data

Register 2 (HE0D2)

R: HE0R27 HE0R26 HE0R25 HE0R24 HE0R23 HE0R22 HE0R21 HE0R20

W: HE0T27 HE0T26 HE0T25 HE0T24 HE0T23 HE0T22 HE0T21 HE0T20

$0033

USB HUB Endpoint 0 Data

Register 3 (HE0D3)

R: HE0R37 HE0R36 HE0R35 HE0R34 HE0R33 HE0R32 HE0R31 HE0R30

W: HE0T37 HE0T36 HE0T35 HE0T34 HE0T33 HE0T32 HE0T31 HE0T30

$0034

USB HUB Endpoint 0 Data

Register 4 (HE0D4)

R: HE0R47 HE0R46 HE0R45 HE0R44 HE0R43 HE0R42 HE0R41 HE0R40

W: HE0T47 HE0T46 HE0T45 HE0T44 HE0T43 HE0T42 HE0T41 HE0T40

$0035

USB HUB Endpoint 0 Data

Register 5 (HE0D5)

R: HE0R57 HE0R56 HE0R55 HE0R54 HE0R53 HE0R52 HE0R51 HE0R50

W: HE0T57 HE0T56 HE0T55 HE0T54 HE0T53 HE0T52 HE0T51 HE0T50

$0036

USB HUB Endpoint 0 Data

Register 6 (HE0D6)

R: HE0R67 HE0R66 HE0R65 HE0R64 HE0R63 HE0R62 HE0R61 HE0R60

W: HE0T67 HE0T66 HE0T65 HE0T64 HE0T63 HE0T62 HE0T61 HE0T60

$0037

USB HUB Endpoint 0 Data

Register 7 (HE0D7)

R: HE0R77 HE0R76 HE0R75 HE0R74 HE0R73 HE0R72 HE0R71 HE0R70

W: HE0T77 HE0T76 HE0T75 HE0T74 HE0T73 HE0T72 HE0T71 HE0T70

$0038

Unimplemented

R:

W:

$0039

Unimplemented

R:

W:

$003A

PLL Control Register

(PCTL)

R:

PLLIE

PLLF

PLLON

BCS

PRE1

PRE0

0

0

W:

$003B

PLL Bandwidth Control Register

(PBWC)

R:

AUTO

LOCK

ACQ

0

0

0

0

0

W:

$003C

PLL Multiplier Select Register High

(PMSH)

R:

MUL11

MUL10

MUL9

MUL8

W:

$003D

PLL Multiplier Select Register Low

(PMSL)

R:

MUL7

MUL6

MUL5

MUL4

MUL3

MUL2

MUL1

MUL0

W:

$003E

Unimplemented

R:

W:

$003F

PLL Reference Divider Select

Register (PRDS)

R:

RDS3

RDS2

RDS1

RDS0

W:

Addr.

Name

Bit 7

6

5

4

3

2

1

Bit 0

= Unimplemented

R

= Reserved

Figure 2-2. Control, Status, and Data Registers (Continued)