5 condition code register (ccr), Condition code register (ccr) – Freescale Semiconductor MC68HC08KH12 User Manual

Page 57

MC68HC(7)08KH12

—

Rev. 1.1

Advance Information

Freescale Semiconductor

57

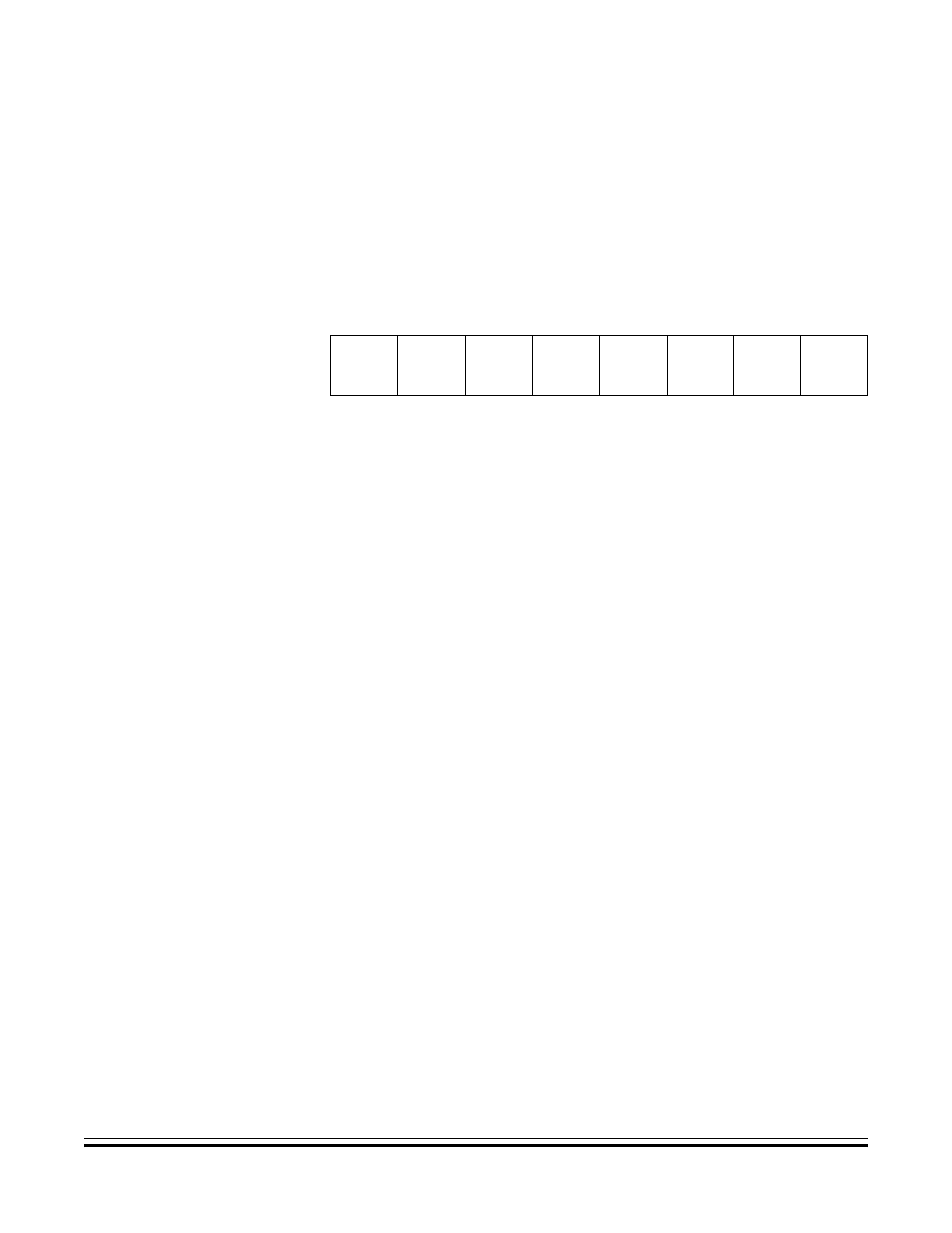

6.4.5 Condition Code Register (CCR)

The 8-bit condition code register contains the interrupt mask and five

flags that indicate the results of the instruction just executed. Bits 6 and

5 are set permanently to logic one. The following paragraphs describe

the functions of the condition code register.

V — Overflow Flag

The CPU sets the overflow flag when a two's complement overflow

occurs. The signed branch instructions BGT, BGE, BLE, and BLT use

the overflow flag.

1 = Overflow

0 = No overflow

H — Half-Carry Flag

The CPU sets the half-carry flag when a carry occurs between

accumulator bits 3 and 4 during an ADD or ADC operation. The half-

carry flag is required for binary-coded decimal (BCD) arithmetic

operations. The DAA instruction uses the states of the H and C flags

to determine the appropriate correction factor.

1 = Carry between bits 3 and 4

0 = No carry between bits 3 and 4

Bit 7

6

5

4

3

2

1

Bit 0

Read:

V

1

1

H

I

N

Z

C

Write:

Reset:

X

1

1

X

1

X

X

X

X = Indeterminate

Figure 6-6. Condition Code Register (CCR)