6 usb embedded device status register (dsr), Usb embedded device status register (dsr) – Freescale Semiconductor MC68HC08KH12 User Manual

Page 144

Advance Information

MC68HC(7)08KH12

—

Rev. 1.1

144

Freescale Semiconductor

1 = The data buffers are used for embedded device Endpoint 2

0 = The data buffers are used for embedded device Endpoint 1

TX1E — Embedded Device Endpoint 1/2 Transmit Enable

This read/write bit enables a transmit to occur when the USB Host

controller sends an IN token to Endpoint 1 or Endpoint 2 of the

embedded device. The appropriate endpoint enable bit, ENABLE1 or

ENABLE2 bit in the DCR2 register, should also be set. Software

should set the TX1E bit when data is ready to be transmitted. It must

be cleared by software when no more data needs to be transmitted.

If this bit is 0 or the TXD1F is set, the USB will respond with a NAK

handshake to any Endpoint 1 or Endpoint 2 directed IN tokens. Reset

clears this bit.

1 = Data is ready to be sent.

0 = Data is not ready. Respond with NAK.

TP1SIZ3-TP1SIZ0 — Embedded Device Endpoint 1/2 Transmit Data

Packet Size

These read/write bits store the number of transmit data bytes for the

next IN token request for embedded device Endpoint 1 or Endpoint 2.

These bits are cleared by reset.

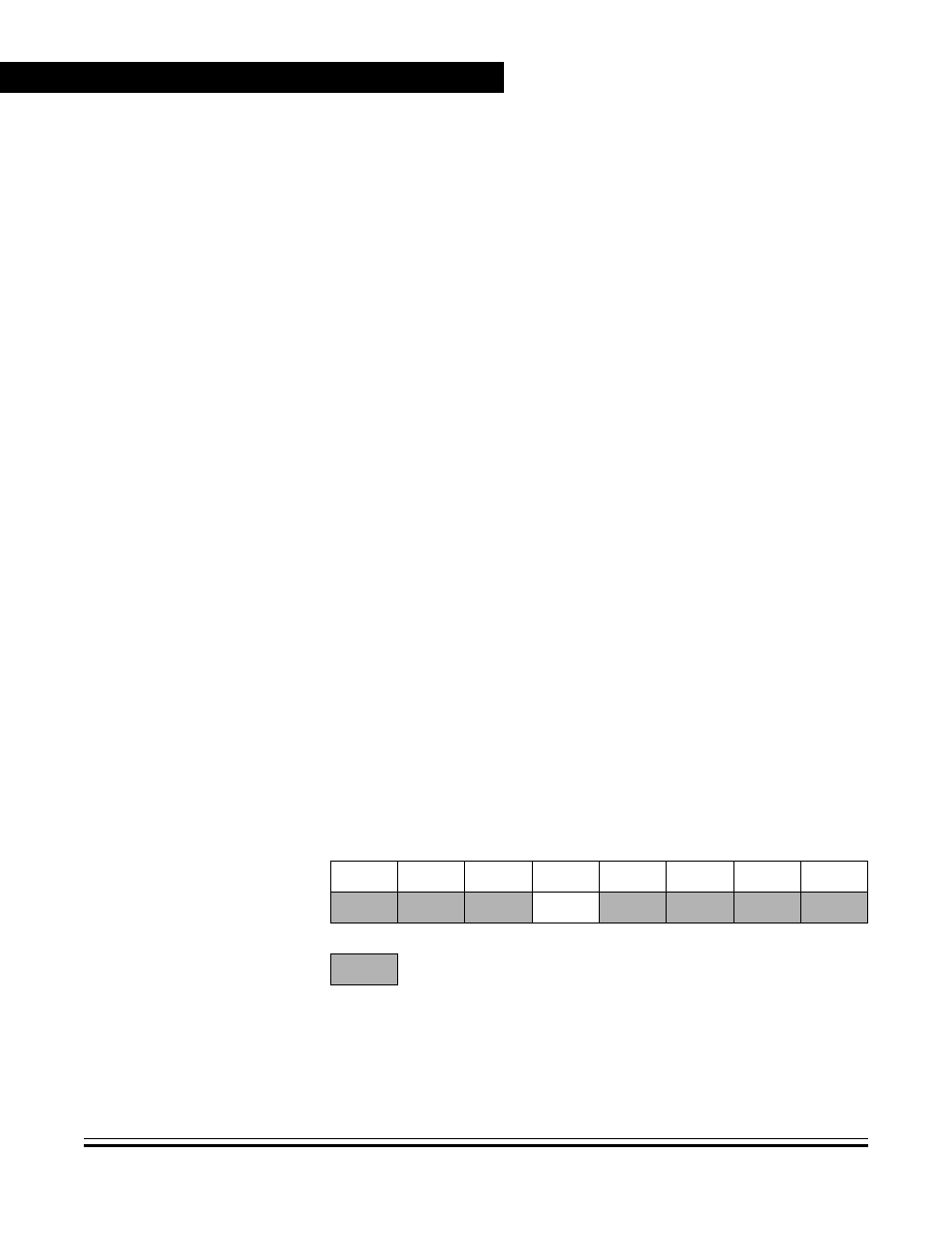

9.5.6 USB Embedded Device Status Register (DSR)

Address:

$004D

Bit 7

6

5

4

3

2

1

Bit 0

Read: DRSEQ

DSETUP DTX1ST

0

RP0SIZ3 RPS0IZ2 RP0SIZ1 RP0SIZ0

Write:

DTX1STR

Reset:

X

X

0

0

X

X

X

X

= Unimplemented

X = Indeterminate

Figure 9-17. USB Embedded Device Status Register (DSR)