Tim status and control register (tsc) – Freescale Semiconductor MC68HC08KH12 User Manual

Page 174

Advance Information

MC68HC(7)08KH12

—

Rev. 1.1

174

Freescale Semiconductor

•

Resets the TIM counter

•

Prescales the TIM counter clock

TOF — TIM Overflow Flag Bit

This read/write flag is set when the TIM counter resets to $0000 after

reaching the modulo value programmed in the TIM counter modulo

registers. Clear TOF by reading the TIM status and control register

when TOF is set and then writing a logic zero to TOF. If another TIM

overflow occurs before the clearing sequence is complete, then

writing logic zero to TOF has no effect. Therefore, a TOF interrupt

request cannot be lost due to inadvertent clearing of TOF. Reset

clears the TOF bit. Writing a logic one to TOF has no effect.

1 = TIM counter has reached modulo value

0 = TIM counter has not reached modulo value

TOIE — TIM Overflow Interrupt Enable Bit

This read/write bit enables TIM overflow interrupts when the TOF bit

becomes set. Reset clears the TOIE bit.

1 = TIM overflow interrupts enabled

0 = TIM overflow interrupts disabled

TSTOP — TIM Stop Bit

This read/write bit stops the TIM counter. Counting resumes when

TSTOP is cleared. Reset sets the TSTOP bit, stopping the TIM

counter until software clears the TSTOP bit.

1 = TIM counter stopped

0 = TIM counter active

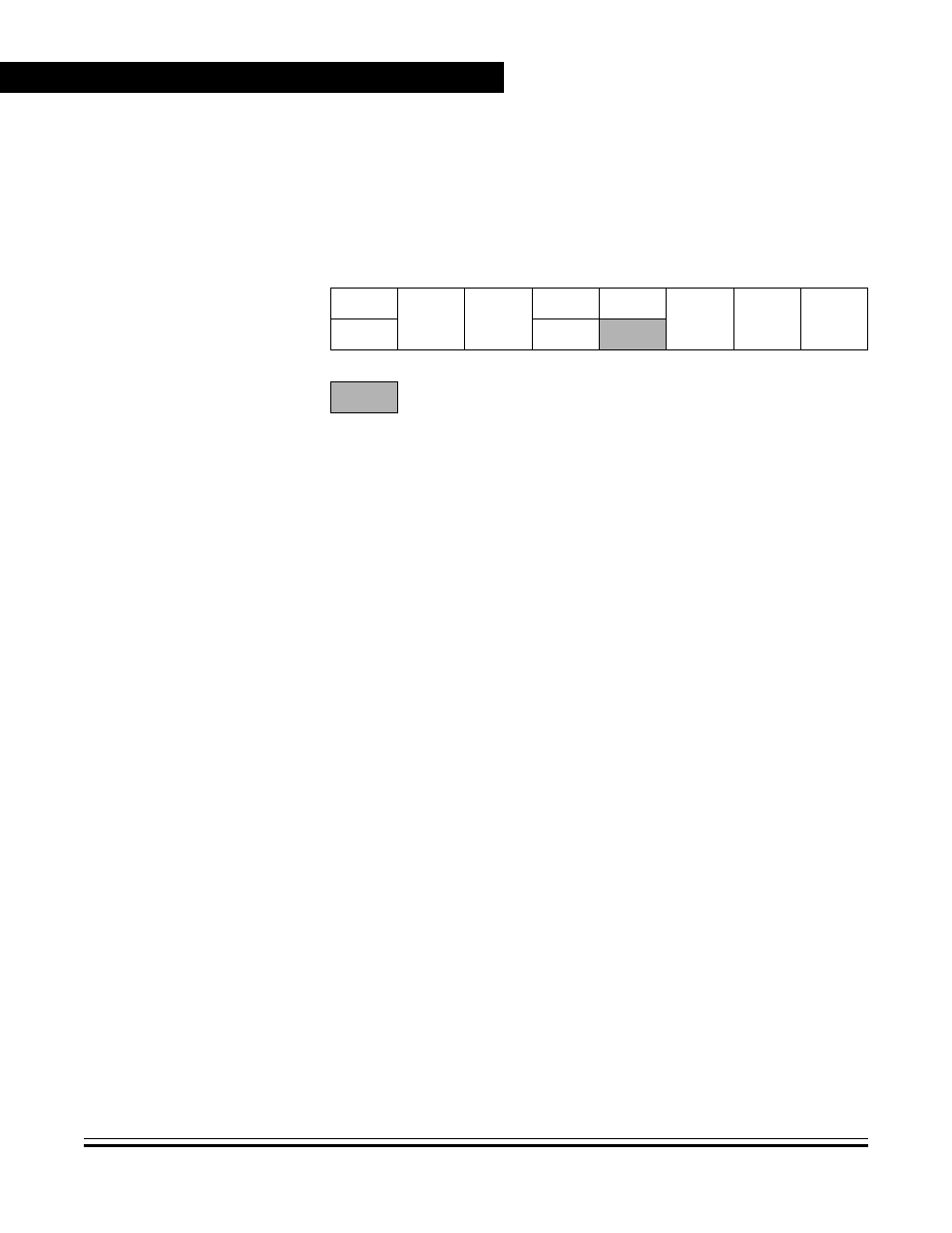

Address:

$0010

Bit 7

6

5

4

3

2

1

Bit 0

Read:

TOF

TOIE

TSTOP

0

0

PS2

PS1

PS0

Write:

0

TRST

Reset:

0

0

1

0

0

0

0

0

= Unimplemented

Figure 11-3. TIM Status and Control Register (TSC)