2 swi instruction, 2 interrupt status registers, Swi instruction – Freescale Semiconductor MC68HC08KH12 User Manual

Page 76: Interrupt status registers, Interrupt sources

Advance Information

MC68HC(7)08KH12

—

Rev. 1.1

76

Freescale Semiconductor

7.6.1.2 SWI Instruction

The SWI instruction is a non-maskable instruction that causes an

interrupt regardless of the state of the interrupt mask (I bit) in the

condition code register.

NOTE:

A software interrupt pushes PC onto the stack. A software interrupt does

not push PC – 1, as a hardware interrupt does.

7.6.2 Interrupt Status Registers

The flags in the interrupt status registers identify maskable interrupt

sources.

summarizes the interrupt sources and the interrupt

status register flags that they set. The interrupt status registers can be

useful for debugging.

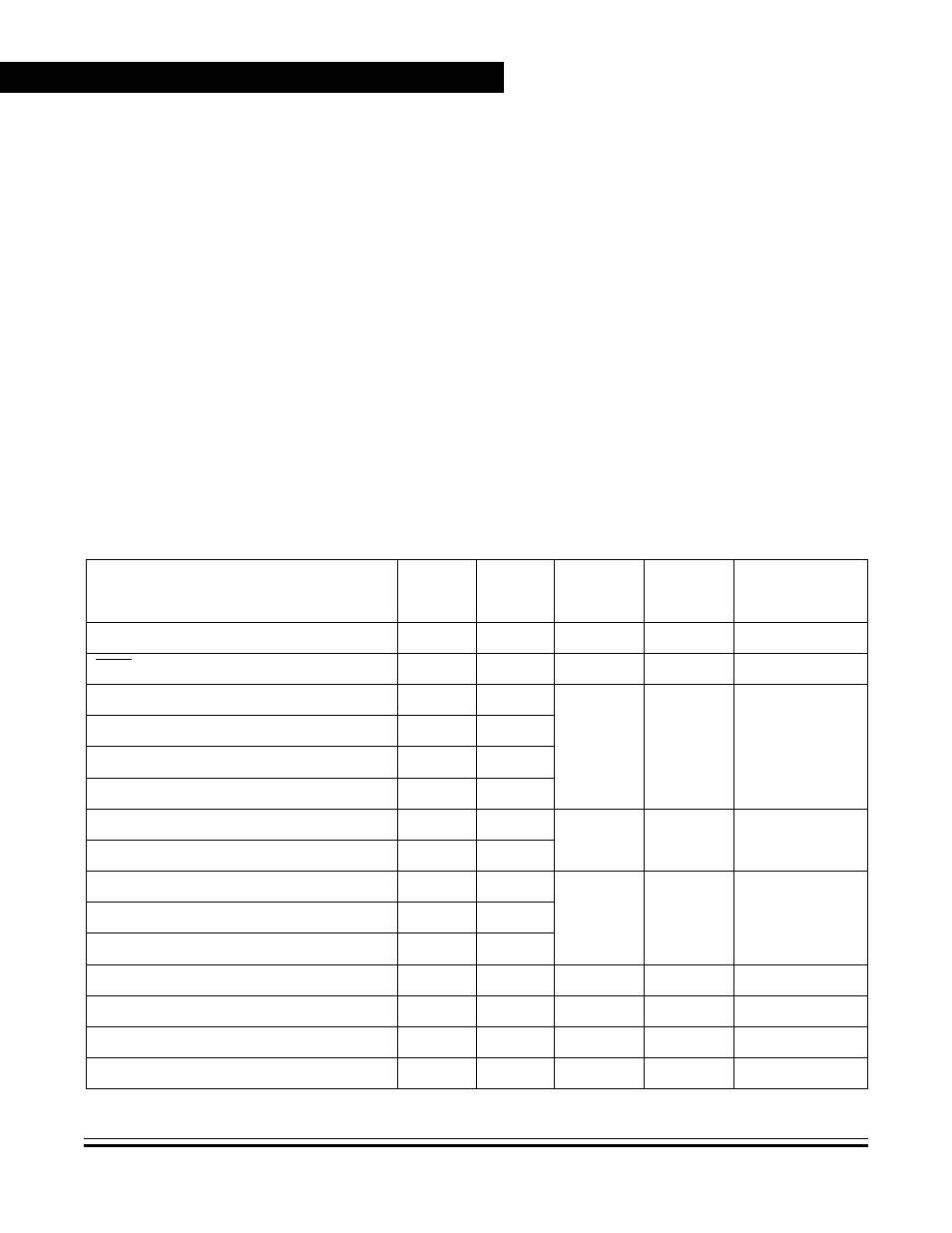

Table 7-3. Interrupt Sources

Source

Flag

Mask

(1)

INT

Register

Flag

Priority

(2)

Vector Address

SWI Instruction

—

0

$FFFC–$FFFD

IRQ1 Pin

IRQF1

IMASK1

IF1

1

$FFFA–$FFFB

HUB Start of Frame Interrupt

SOFF

SOFIE

IF2

2

$FFF8–$FFF9

HUB 2nd End of Frame Point Interrupt

EOF2F

EOF2IE

HUB End of Packet Interrupt

EOPF

EOPIE

HUB Bus Signal Transition Detect Interrupt

TRANF

TRANIE

HUB Endpoint0 Transmit Interrupt

TXDF

TXDIE

IF3

3

$FFF6–$FFF7

HUB Endpoint0 Receive Interrupt

RXDF

RXDIE

Device Endpoint 0 Transmit Interrupt

TXD0F

TXD0IE

IF4

4

$FFF4–$FFF5

Device Endpoint 0 Receive Interrupt

RXD0F

RXD0IE

USB Endpoint1/2 Transmit Interrupt

TXD1F

TXD1IE

TIM Channel 0

CH0F

CH0IE

IF5

5

$FFF2–$FFF3

TIM Channel 1

CH1F

CH1IE

IF6

6

$FFF0–$FFF1

TIM Overflow

TOF

TOIE

IF7

7

$FFEE–$FFEF

Port-E Keyboard Pin Interrupt

KEYEF

IMASKE

IF8

8

$FFEC–$FFED